Hi together,

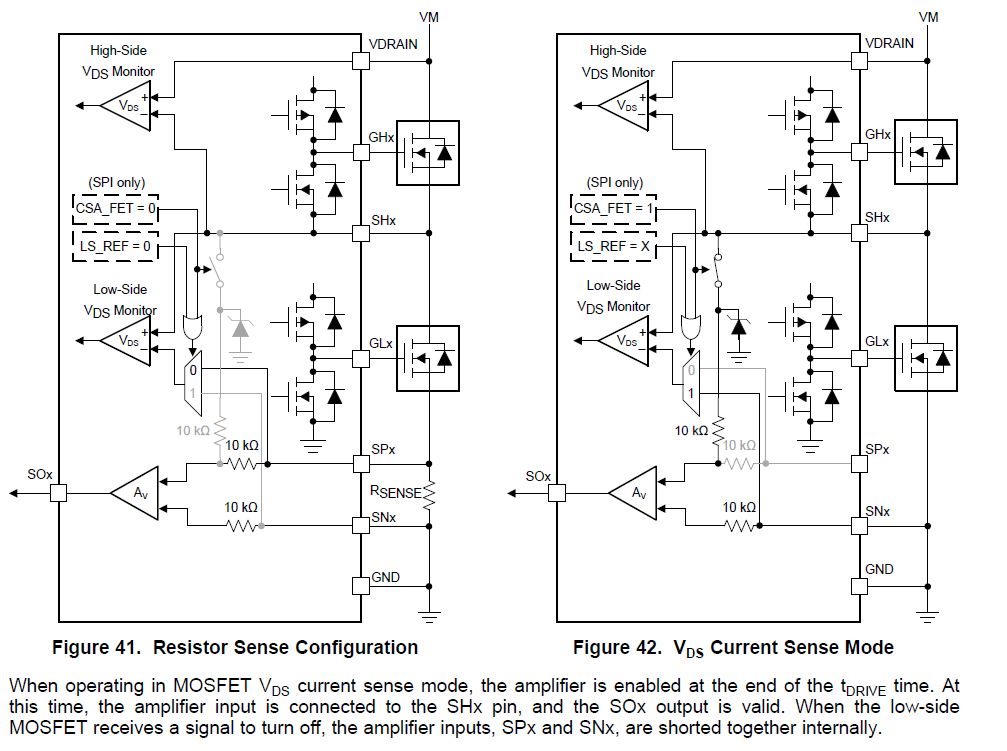

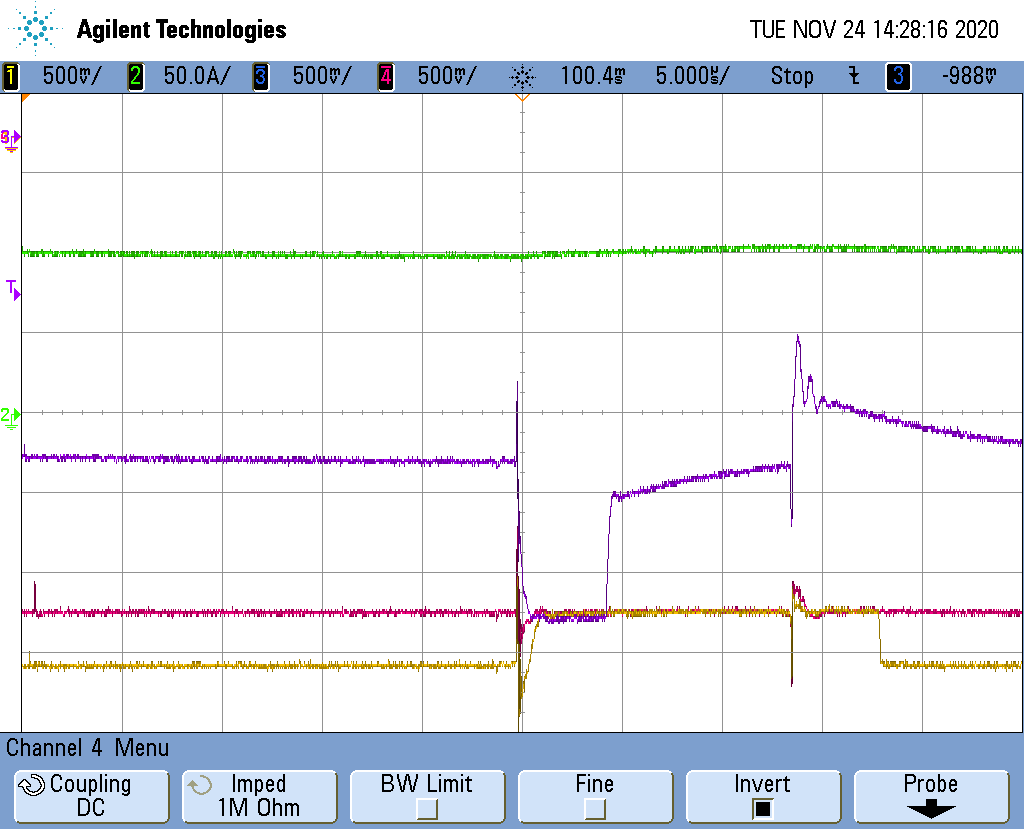

I have some voltages anomalies at the current sense outputs of my design. I'm using the measurement over the rds_on (SH_x, SNx).

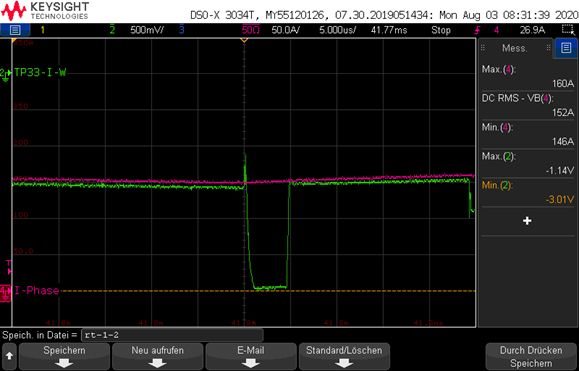

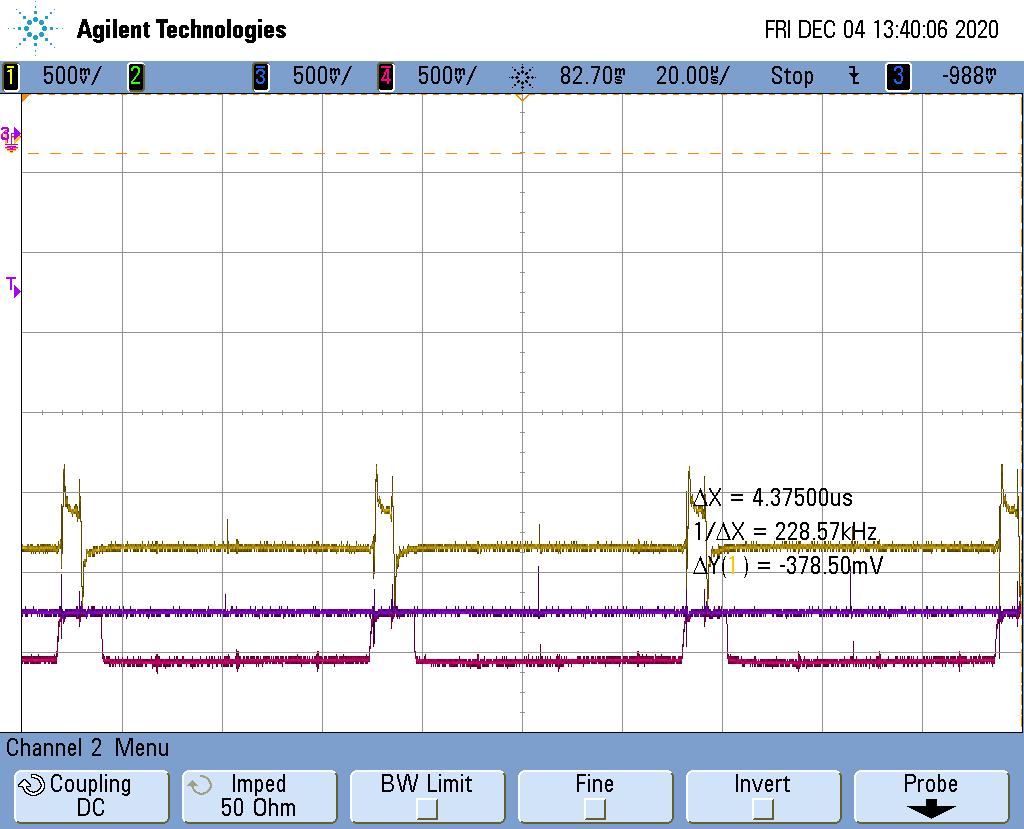

At higher currents the output goes to "0" (=3V) for 5µs, afterwards the signal ist back as expected. The phase current doesn't have these spikes, so the driver seem to work.

Spikes start at ~80A phase current.

Green is the voltage on SOB,

Red is the current measured with clamp meter.

The DIS_SEN =1b, so the fault is ignored. Is there another protection of the SOA output? Or can you explain what happen in these 5µs?

Rgds Martin