Other Parts Discussed in Thread: TMS320F280049C

Hi all

My customer has below question for the DRV8323S, please comment and clarify.

Best regards

Ueli

--------------------------------------------------

We are currently facing an issue, when trying to write on the driver registers via SPI.

Below the procedure that we followed. Please note that the 3 « LOCK » bits located in Gate Drive HS Register are configured so that registers can be modified (011b).

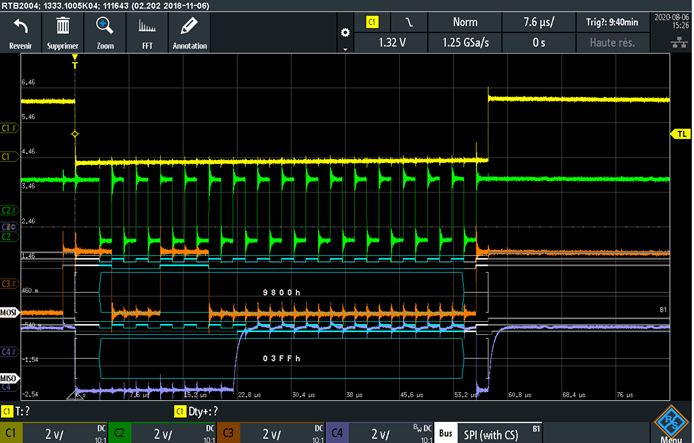

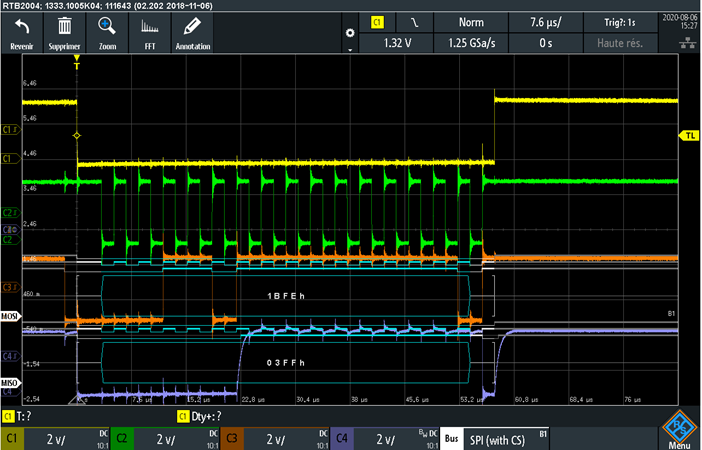

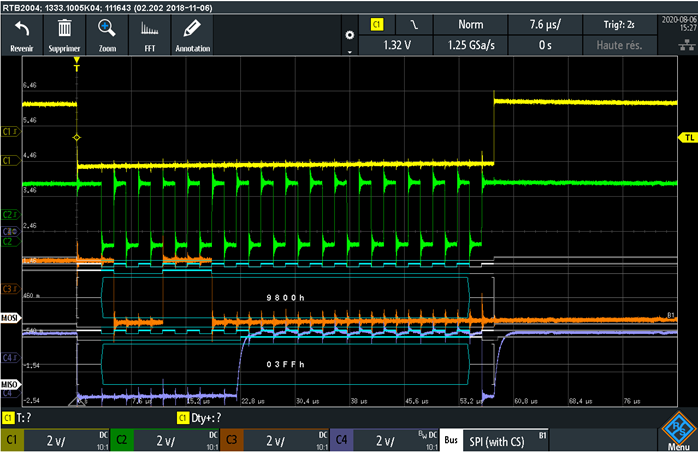

Channel C1 : Chip Select

Channel C2 : Clock (300kHz)

Channel C3 : MOSI

Channel C4 : MISO

- Reading Gate Drive HS Register (adress 0x03) : we send 0x9800 on the bus

- Changing IDRIVEN_HS value from 2000mA (1111b, default value) to 1640mA (1110b) : we send 0x1bfe on the bus

- Reading modified Gate Drive HS Register : we send again 0x9800 on the bus à NO CHANGE (driver should have sent back 0x03fe)

Are we doing something wrong ? Any other lock bits to be configured ?