Hello,

In relation to this post, if there is an internal ESD protection diode or internal parasitic diode between nSLEEP pin and VM pin in DRV8889-Q1, I wonder whether a current runs from the nSLEEP pin through the VM pin when a VM voltage drops below 5 V while that 5 V is applied to the nSLEEP pin by an external MCU, for example. I'd like to know if it could happen.

Wang5577 said:4. I don't see a requirement for a sequencer. But, before nSLEEP pin is pulled high, VM input voltage should be stable. After nSLEEP pin is pulled high at VM>UVLO, please give 0.9ms wake-up time, and then, send signals to DRV8889-Q1. nSLEEP pull-up source cannot use DRV8889-Q1's DVDD.

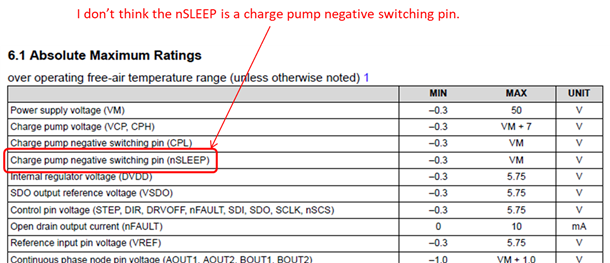

What's the absolute Max rating of the nSLEEP pin? I wonder if there's something wrong with the Absolute Max Ratings in the data sheet. My question above assumes that the nSLEEP pin's absolute Max voltage is VM.

Best regards,

Shinichi Yokota