Hi

1. We have 8 motors, 1 to 4 of which is SPI in series for control, and 5 to 8 of which is another SPI for control. /Is there any precautions for this application?

2.DRV8889's 18Pin:Step, 19Pin:DIR, 20Pin:DRVOFF are suspended. All three functions are controlled by the CTRL3 register./Is the application appropriate?

3.EMI design: The capacitance between each phase output by DRV8889 two phases is 10nF, and a 10nF capacitor is pulled to the ground below each phase./Are there any other points to be noted in addition to the tuning rate for EMI design?

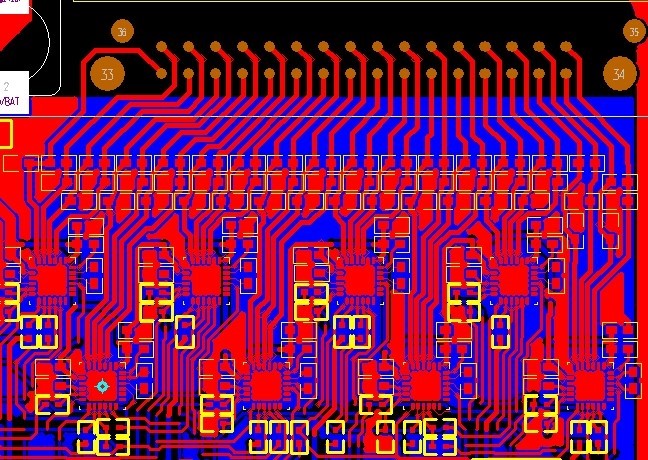

4.Layout: Are there any matters needing attention?

Thanks!