Other Parts Discussed in Thread: DRV8343-Q1

Hi,

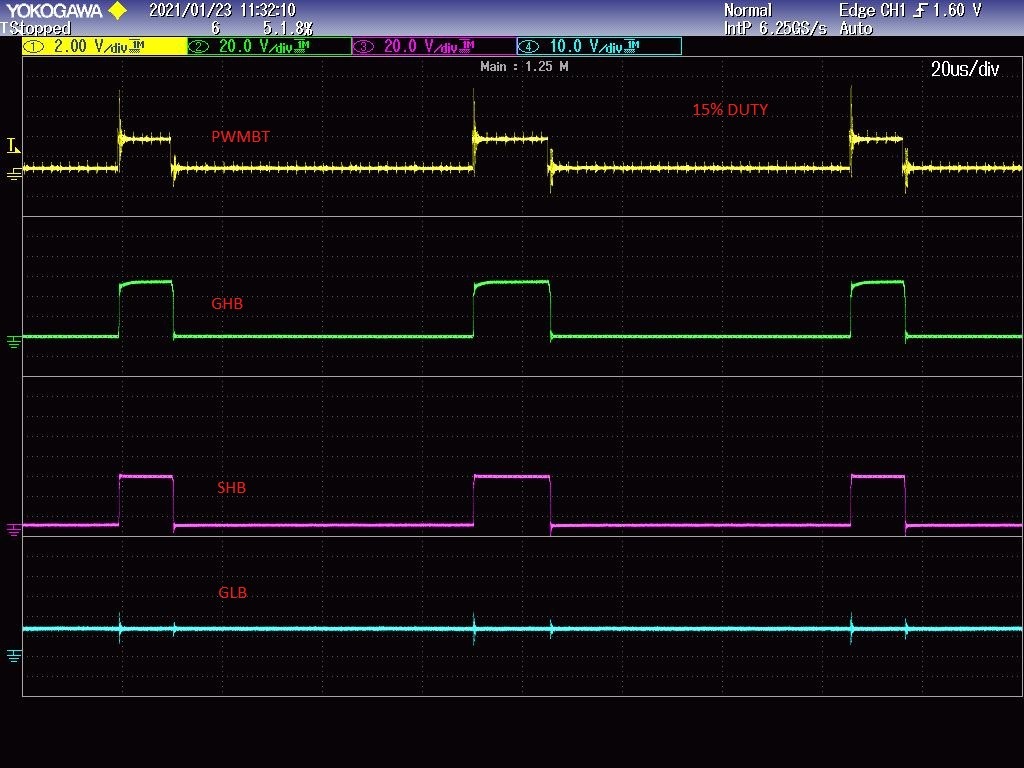

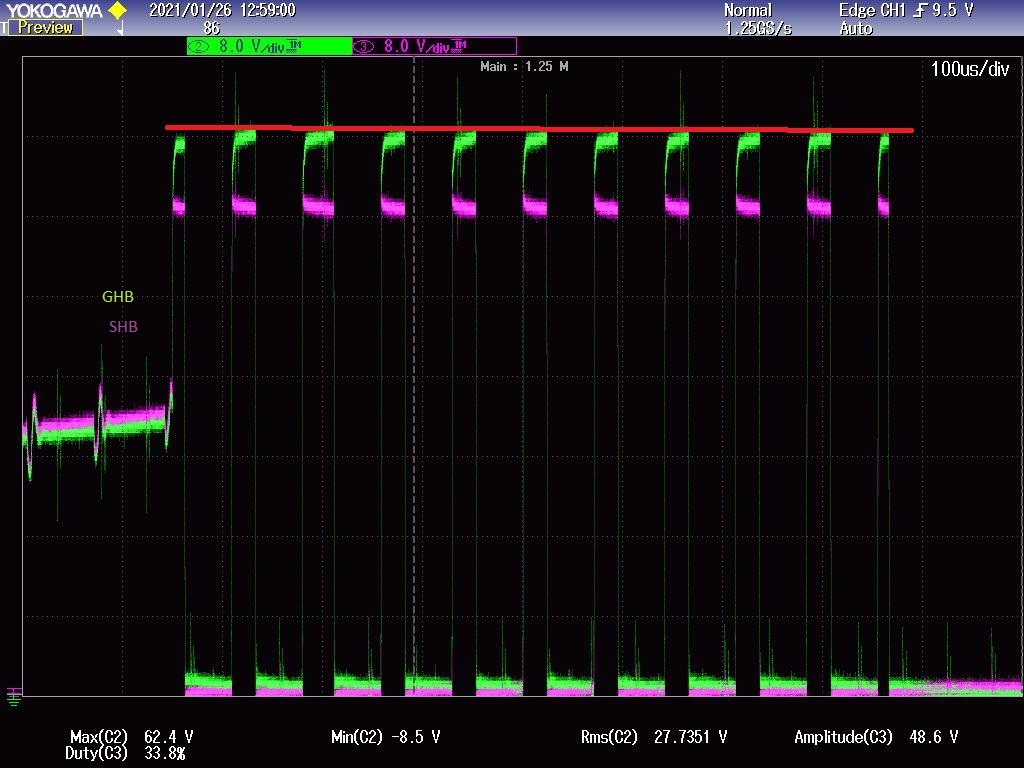

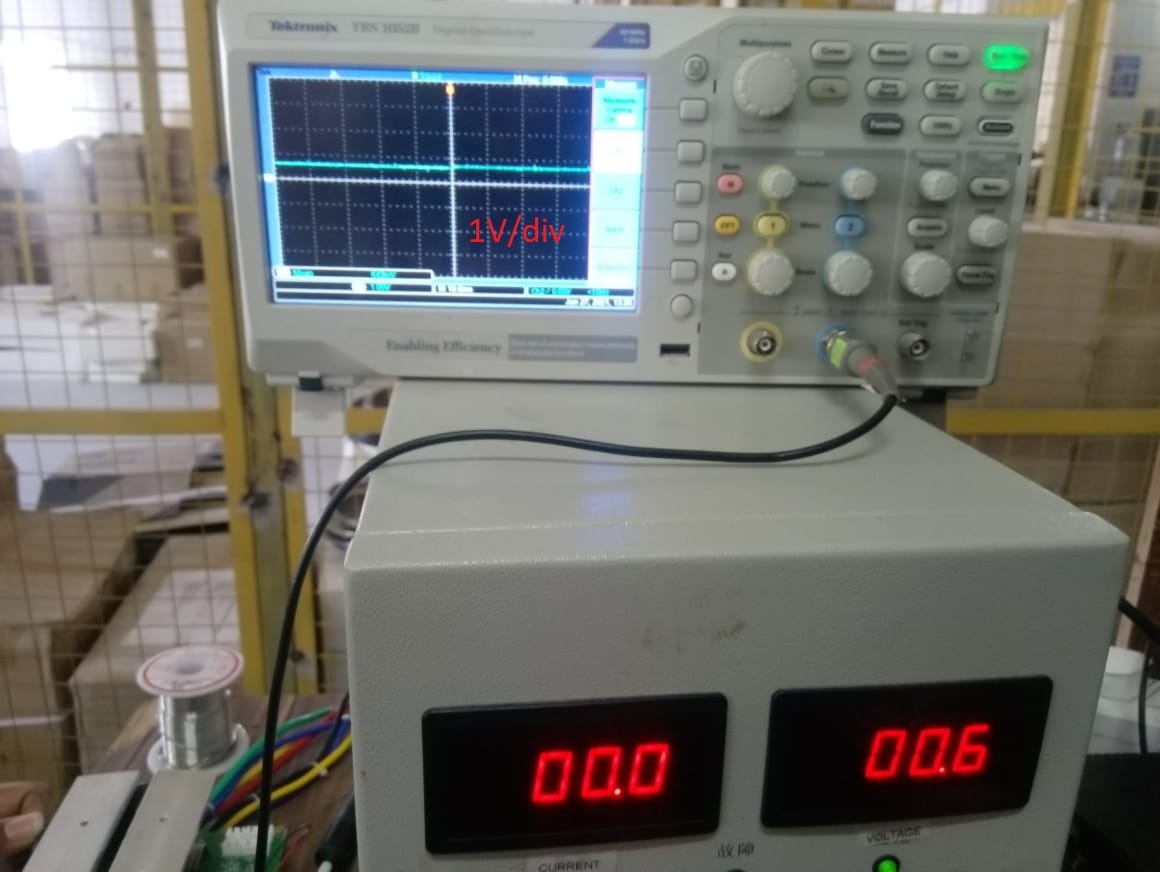

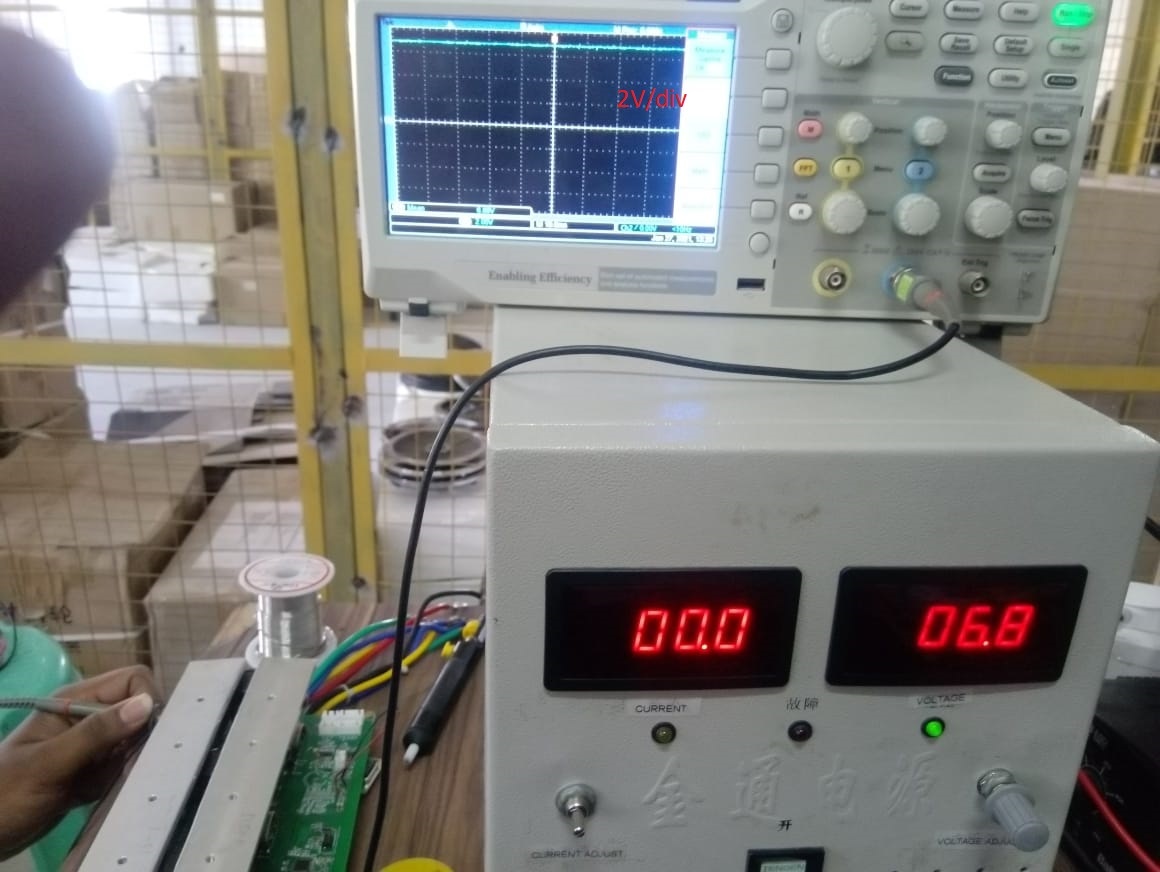

I am using drv8353 and delfino for controlling 3 phase SRM motor with hall sensor feedback for position measurement. I am able to rotate the motor in no load. In load the over current fault occurs even with low load. In no load also, the 3 phase currents are not equal. Anyone having experience with SRM motor control, kindly help me to solve this problem.

Note: feedback - magnet disc is attached with shaft and hall sensor is placed against it.