Other Parts Discussed in Thread: DRV8323

Hi Team,

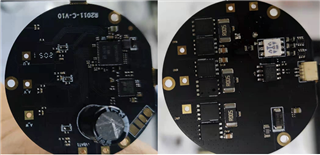

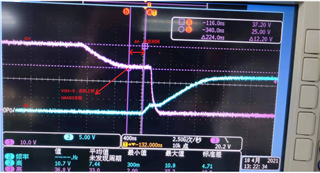

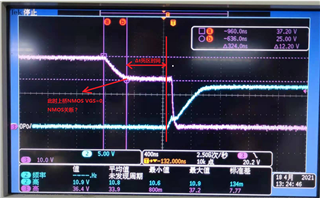

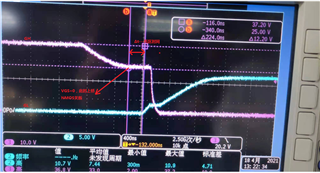

The customer used DRV8323RH to drive the motor. The target motor with blades can reach more than 5000 rpm, but actually it can’t go up to 4600 rpm. The external power supply is 20V, about 18A.

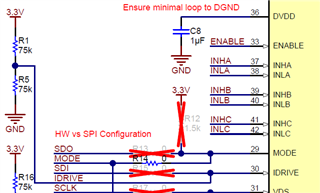

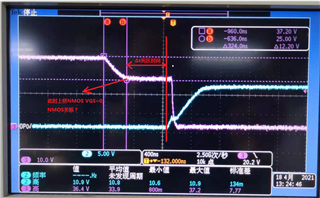

He changed the gain from 10 times to 5 times (the gain pin pulls down the 45.3K resistance into the ground to directly ground) . The customer assumes that the gain is doubled, and the current of each phase of the three-phase motor should also be doubled. However, it is actually measured that the maximum speed of the motor with blades can only reach 4800 rpm. At this time, the external power supply is 20V/20A.

Customer would like to know how to resolve this case?

Thanks,

Annie