Other Parts Discussed in Thread: LAUNCHXL-F28379D

Hi,

I am developing with BOOST XL-DRV8305EVM and LaunchXL-F28379D.

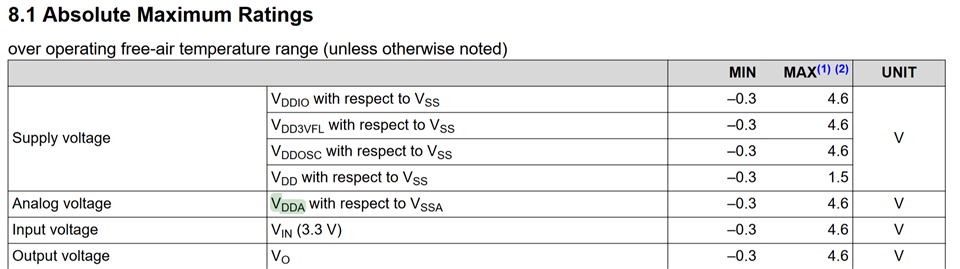

From 8.2.2.4 Current Sense Amplifiers in the URL below, the maximum output voltage range is 3.3V.

https://www.tij.co.jp/jp/lit/ds/symlink/drv8305.pdf

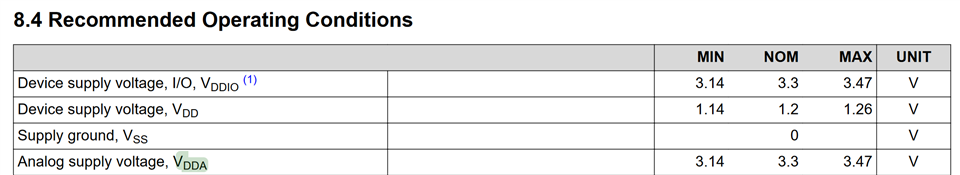

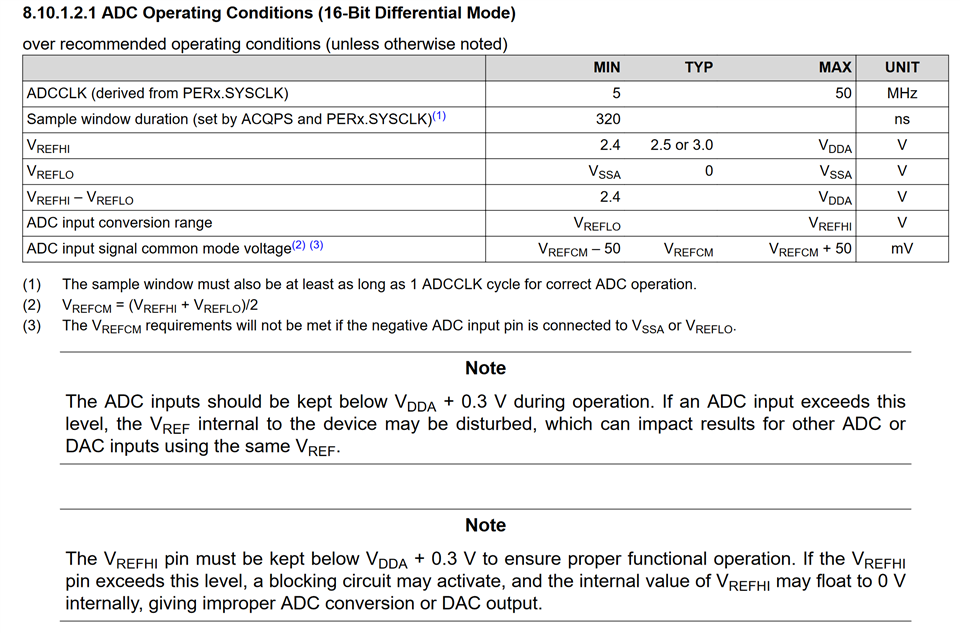

ADC of LaunchXL-F28379D in the latter stage is VREFHI = 3V, so the maximum convertible voltage by the ADC is 3V.

Is this voltage difference a problem in use?

Koki