There are the following problems about the loop stability of TPS53355:

the input voltage is 12V, the output voltage is 5V, and the RMS value of the actual current is 5.66A,Test point is R2552, the schematic diagram is as follows

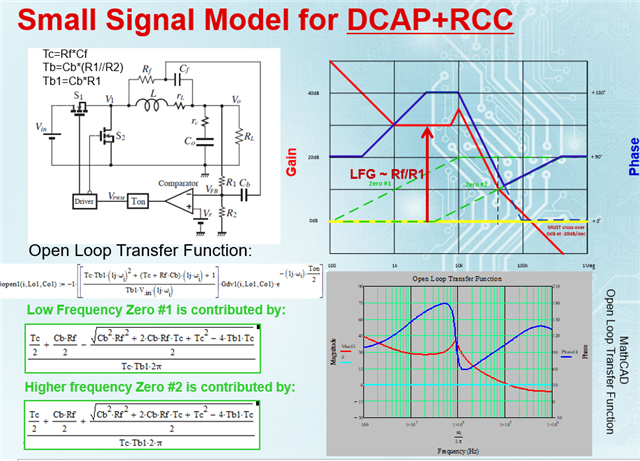

1. The phase does not cross zero, please help to assess the risk and whether it has an impact on the loop stability. At the same time, please give suggestions for improvement.

2. The switching frequency is 500KHz, and the crossing frequency is only 2.35k which is low. Is there any hidden danger and risk that needs to be adjusted? Please also give suggestions for improvement.

Thank you