Dear All,

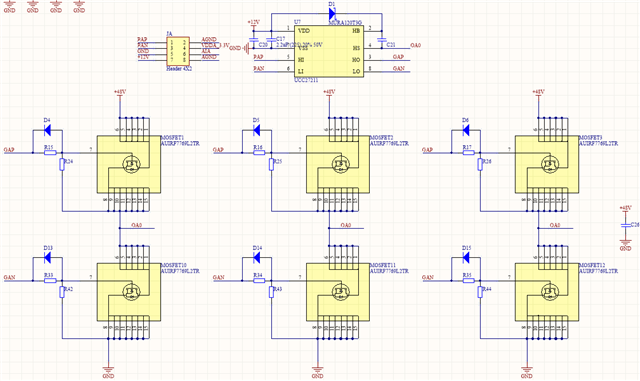

I am using UC27211 for a three-phase motor driver. A UC27211 drives six MOSFET (Part No.: IRF7769L1), three on the upper arm in parallel and three on the lower arm in parallel. The schematic of one phase is shown in Figure 1 below. The bootstrap capacitor is 4.7uF. The turn-on gate resistor is 2Ω. Turn-off gate resistor is ideally 0Ω, by using a reverse diode.

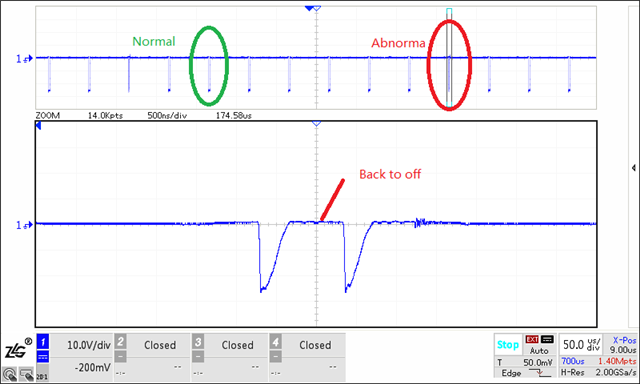

Figure 2 shows the output voltage. Please ignore the negative polarity of the waveform caused by the measurement. The pulse width of the PWM signal is about 1.5us. The normal waveform is good, with fast turn-on and turn off transistion.

However, there is abnormal waveform occasionally observed. It seems that the mosfet is turned-on firstly, then back to off immediately, and then tries to turn-on again. Please note that low voltage means on state.

It can be also observed that the G-S signal is missing occasionally, which causes the abnormal output voltage.

This phenomenon happens when the DC-link voltage increases to 30V. At 20V DC-link, no abnormal waveforms are observed.

Could anyone provide a solution to address this issue? Should I increase the turn-on resistor?

Thanks!

Figure 1: Schematic of the gate driver for six mosfets.

Figure 2: Phase Output Voltage (Please ignore the negative polarity of the waveform caused by the measurement).