Other Parts Discussed in Thread: CSD19531Q5A

Hi there,

We have a board designed for 5.2V 6A and 7.4V 18A output running of 30-48V. We are seeing some failures during operating as well as at power on. There are also boards which work fine and temperatures do not exceed expected values.

In one case the LM5116 chip burnt out and in the other the voltage is lower than expected and the other chip is heating up. Some of the boards are working just fine. Both the 7.4V layouts and 5.2V layouts are very similar and based on the guidelines in the EVAL board: www.ti.com/.../snva285a.pdf

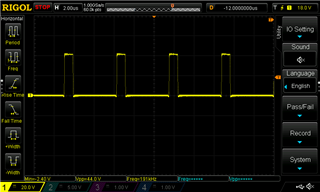

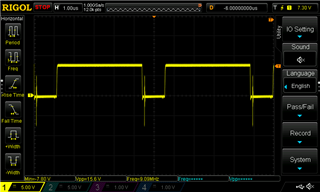

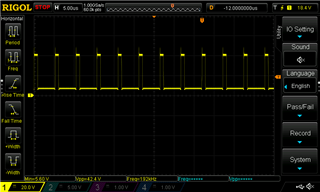

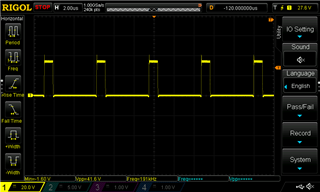

What I am seeing when measuring the HO and LO on the mosfets the LO has a very negative spike at high currents and I am wondering if this is the cause of the failures? It seems that some negative transient here is inevitable according to the posts I have been reading. Is there anyway to verify that this is what has been causing the LM5116 failures e.g by measuring the failed chips in some way?

I also noticed our CSD19531Q5A mosfet 226nC QRR is relatively high, could this be causing the negative spikes?

HO, LO, SW (pin 20), HB (pin 18)

I think the component selection and layout should be okay as per the excel design, I have attached them as well for reference.