Other Parts Discussed in Thread: TPS61240

Hi team,

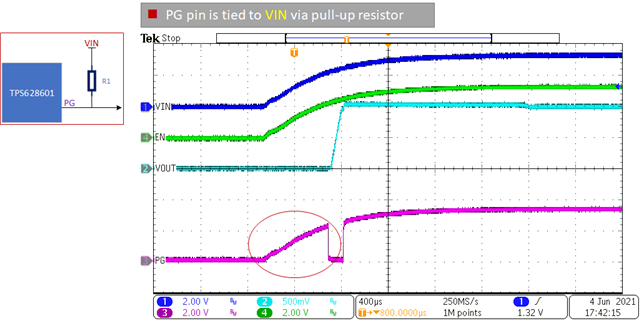

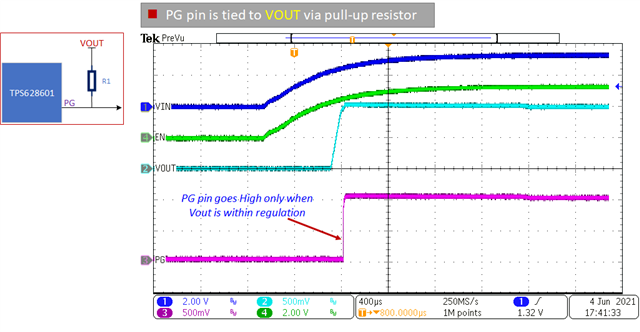

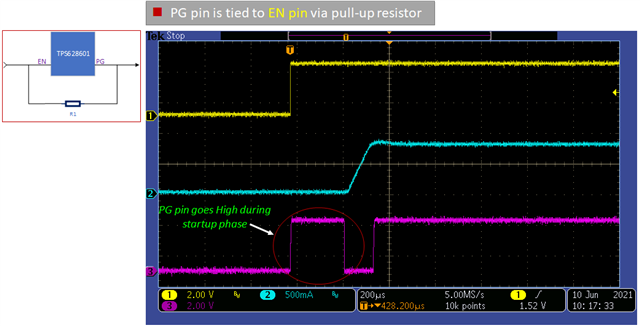

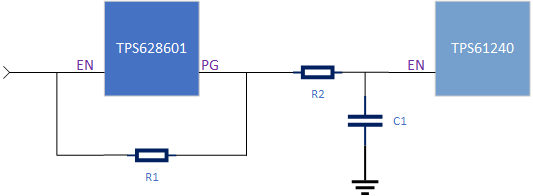

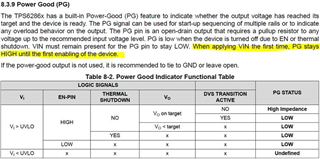

My customer would like to use the TPS628601 power good signal drive the enable of the TPS61240 to sequence the two power rails. Section 8.3.9 in the DS says that the signal can be used for just that purpose. However further down in that section it states that it doesn’t actually work until the device is enabled (see yellow highlight below). The design requires an I/O signal to control the power enable (i.e. we can just tie the enable to Vin).

So is section 8.3.9 accurate? If so, is there any recommended work around? The design is a very tiny module, and there's no room for adding other ICs such as an external power sequencer.

Regards,

Connie