Hello TI Support Team and Community,

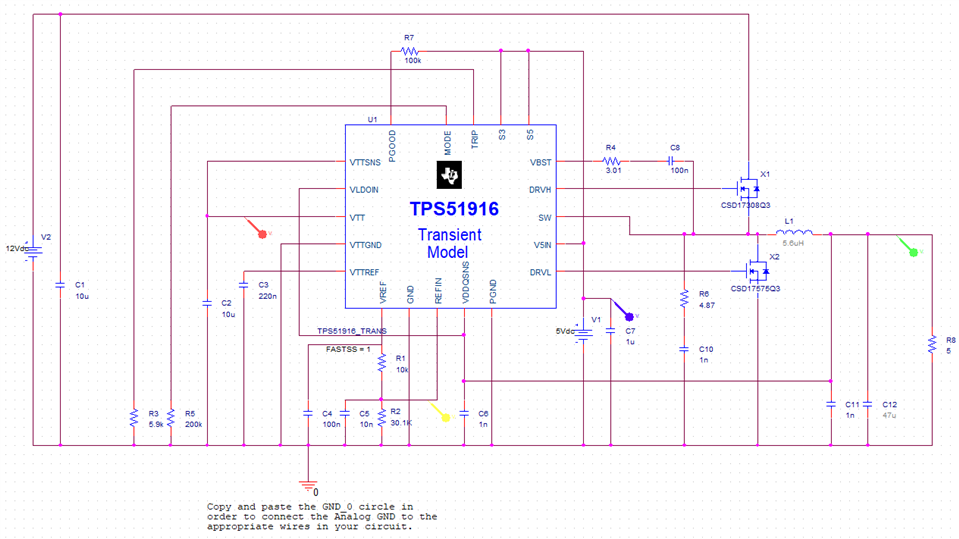

I am working in the standard Cadence PSpice, and not the PSpice for TI variant.

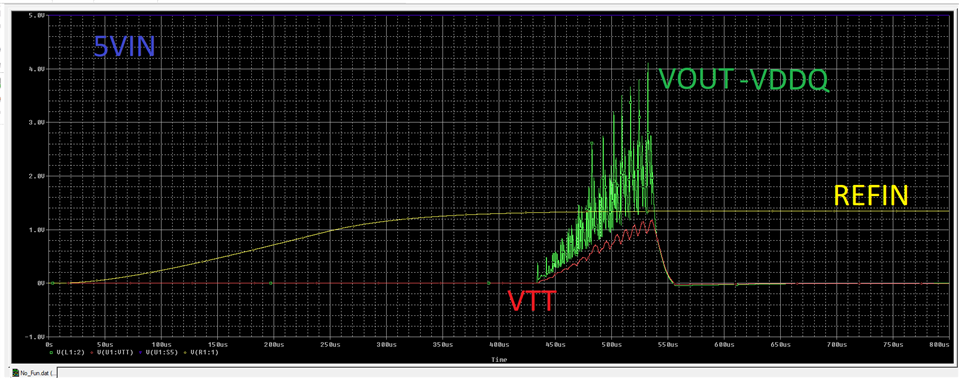

There appears to be an issue with the bias point in my schematic and possibly an issue with the model. The VREF voltage is coming out as 0V, and so no switching is really occurring as the REFIN sees 0V.

This is using the TPS51916 Transient model... So I am unsure how this model needs to be used... When I run a transient, the bias point appears to cause a problem as the REFIN sees 0V. I had to use the auto-convergence in order to even get the simulation to run because there were convergence problems noted within nodes of the TPS51916 model. There are no other complex devices in the schematic that appear to be causing issues...

Would you have any hints about what could be causing this kind of an issue? Are these models only valid in the PSpice for TI variant, and not valid for standard Cadence PSpice?

Thank you in advance.