Design the circuit according to Webench:Vin=11-13V、Vout=0.82V、Iout=20A

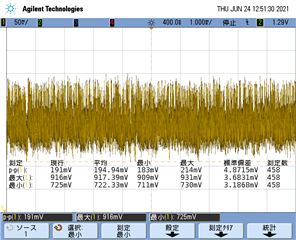

Ripple noise = 200mVp-p, which is very large.

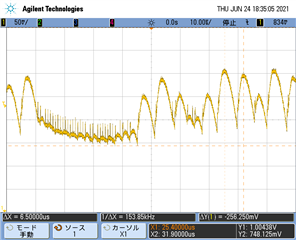

The SW frequency is also unstable.

The actual load is about 1 to 5A, but there is no change in ripple noise.

Also, Vout = 0.85V, which uses the same IC, is more stable.

Are there any possible causes and countermeasures?

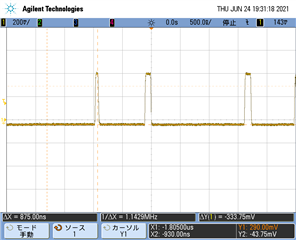

Figure 1:Ripple Waveform

Figure2:Figure1 Zoom

Figure3:SW Waveform