Hello Team,

I got some questions from customer about LM25149-Q1.

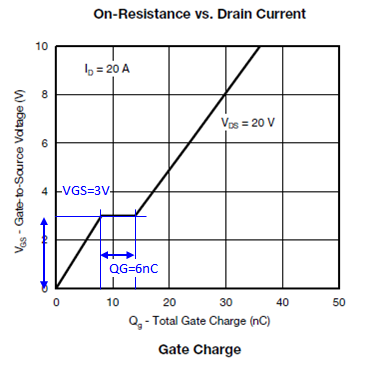

Q. Customer want to use MOSFET(Qg=46nC) and want to output Iout=23.5A. In that case, how much bootstrap capacitance is needed?

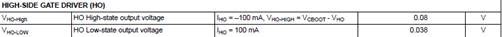

Q. The charge of bootstrap capacitor consume during the HS-FET is ON. Can the bootstrap capacitor re-charge fully during the period of minimum Off time?

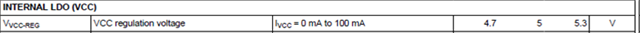

Q. When VIN=4V, how much gate voltage become?

Q. When customer use Qg=46nC MOSFET, how much time of "turn-on" and "turn-off"?

Thanks,

Yuta Kurimoto