Other Parts Discussed in Thread: UC3825

Hi ,Have a good day.

we got a special power requirement that we hope to complete a flyback power supply with a wide voltage output to achieve adjustable output from 0V-250V, and the maximum power is 120W.

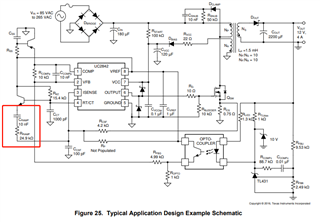

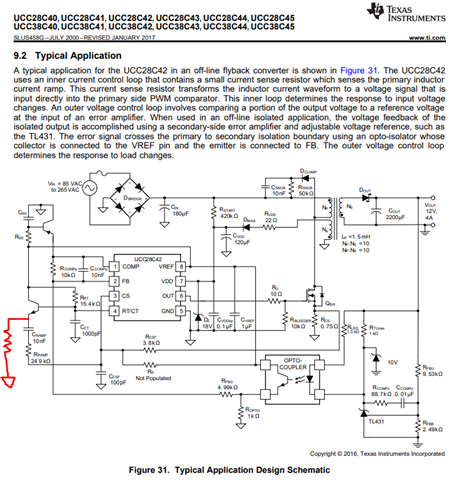

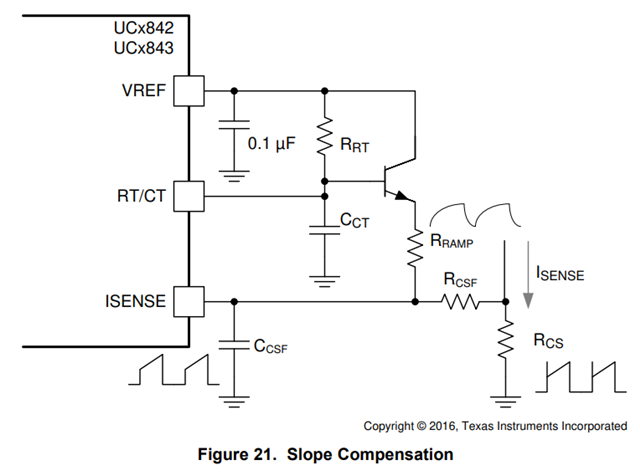

In order to achieve a very small ripple voltage, we hope to avoid entering burst mode on all output voltages,and we chose the UC3843 and we designed the Demo board.

To meet more precise voltage and current control,we put the IC on the second side realized by photoelectric driver and current transformerto .

And we found some questions may need your professional support:

1,Can UC3843 meet our needs not to enter Burst mode? Are there other TI ICs that can be supported?

2,I found that the other companies have implemented this requirement by a flyback with UC3825. Is there any special difference between UC3825 and UC3843 for Burst mode?

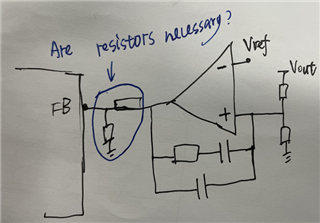

3,We found that our demo board has irregular driving problems. What are the reasons for this problem? We posted the schematic.

4,How should the transformer be designed for this requirement, could you send me your opinion?

Thanks a lot.Flyback.pdf