Hello,

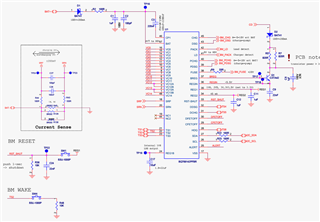

I've a PCB designed for BQ769142 battery manager. I completely followed the TI reference design for connections. At first test, I just wanted to see REG18 output (1.8V internal regulator), and REG1 and REG2 outputs to be sure about working the chip. Then, I just mounted a few elements on my PCB.

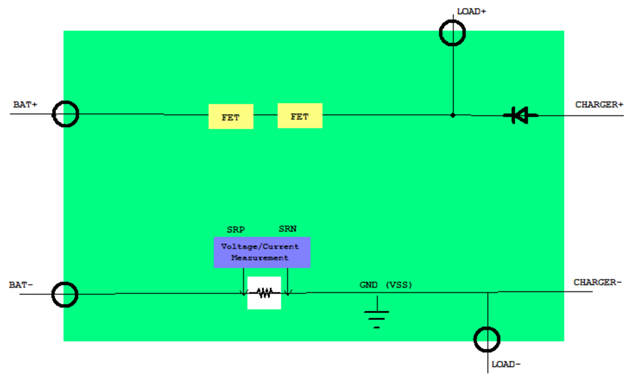

I left almost all pins open (VCx, DSG/CHG/TSx...), just connecting VBAT, CP1, VSS, SRP/SRN, and REGIN-BREG-REG1/2/REG18 (like reference design with their caps, diodes, transistors,...). I connected VBAT to a power supply. Then I started to increase it from 0V to higher values. I noticed that when I reach to around 10V, REG18 is increasing upto 4V, but by datasheet it should not!. REG1 and REG2 are also increasing. BREG is not 5.5V. In VABT around 20V it seems the chip is damaged permanently. I burned 2 chips like that.

What I have done wrong? What is the simplest basic way to see the chip working, like seeing REG18 output, having charge-pump working on CP1... without really connecting it to a multi-cell battery?

Thank you very much