Hi Team,

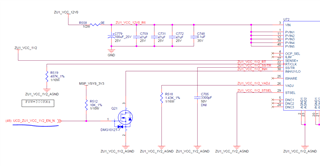

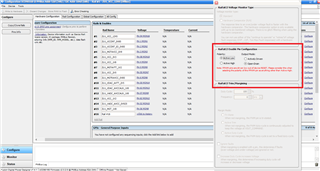

we have used UCD90160A power sequencer in our board. we have used FPWM2/GPIO6 pin to enable the one of the regulator which requires active low enable (by default should be high kept regulator off and should go low while enabling the regulator based on sequence). when i tried to configure this in fusion digital power designer tool seting the pin to active low, its shows me a note as : FPWM pins are driven low out of reset as shown below

later i understand that FPWM pins are driven low upon the reset. My queries are;

1. If this effect my power sequencing if i go with active low configuation on FPWM2/ GPIO6 pin , If the device V33A & V33D are maintained above Vreset(2.4V max) and device reset pin (pin 9) is held high to 3.3V avoiding the reset.

2. In any other possibility except V33A & V33D are below Vreset(2.4V) and RESET pin is low, that FPWM pins goes to reset state (low) and effect the sequencing.

Thanks in Advance,

Kiran