Hello,

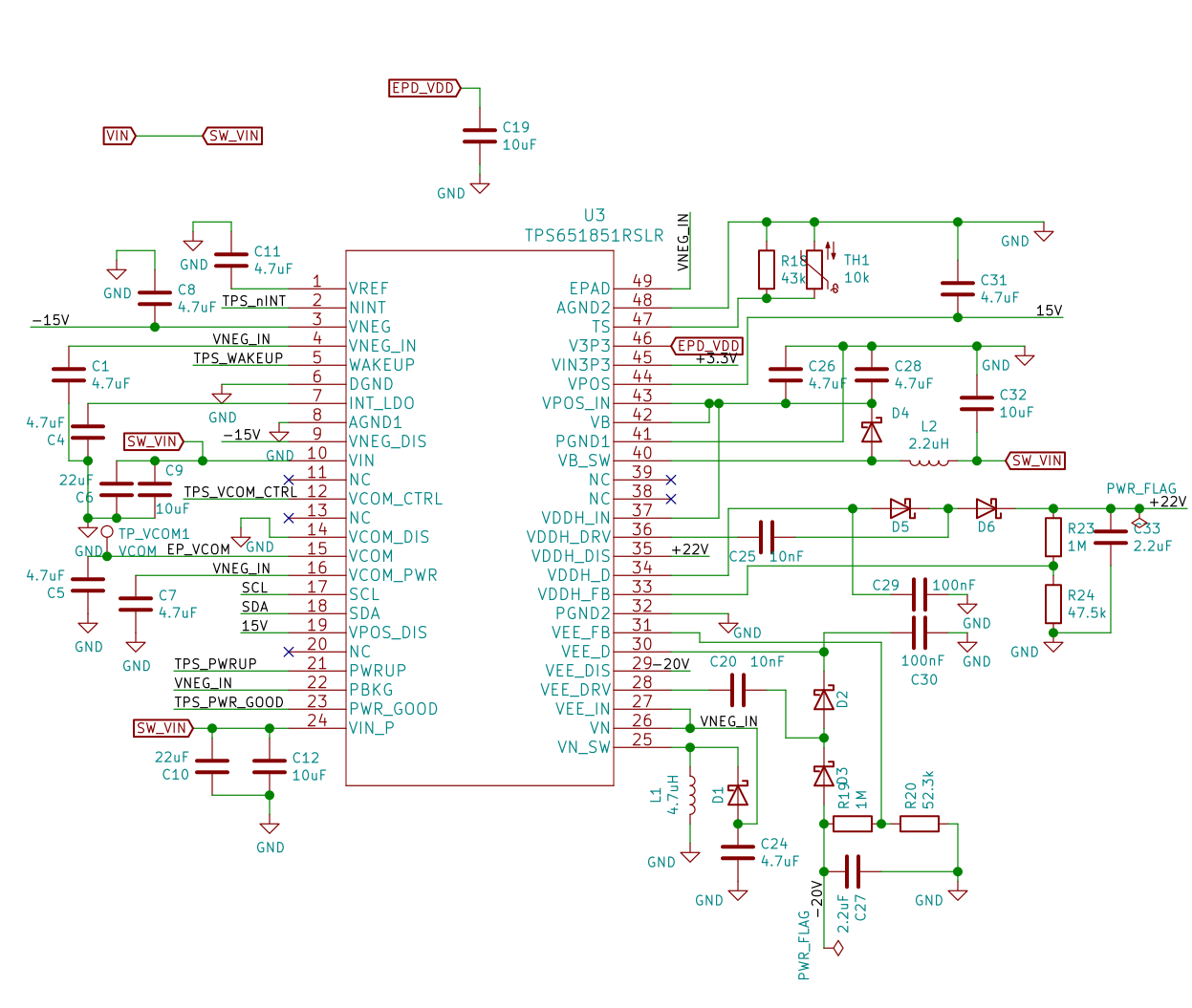

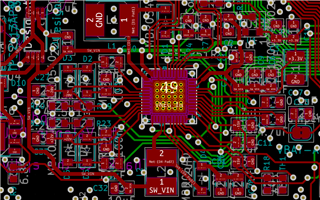

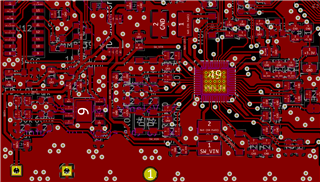

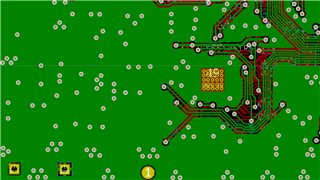

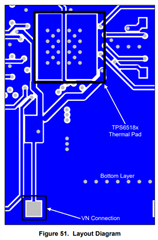

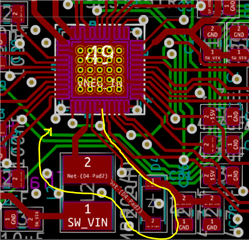

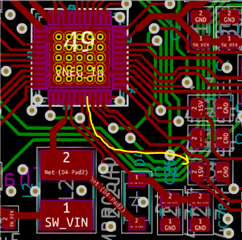

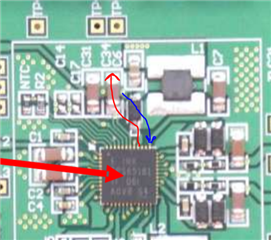

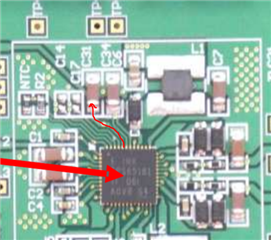

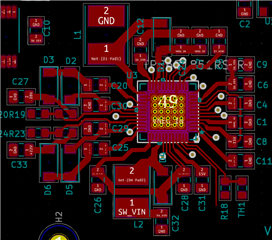

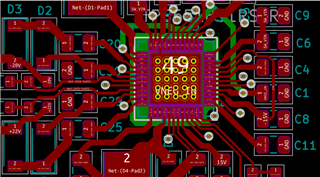

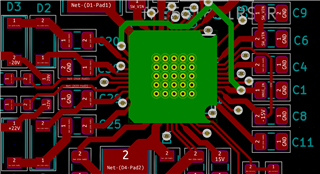

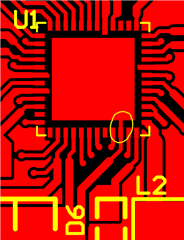

I'm working on a design based on the TPS65185. So far, everything is working well, communication works and all power rails except VPOS have their desired voltage.

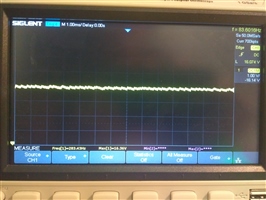

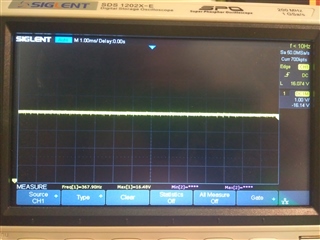

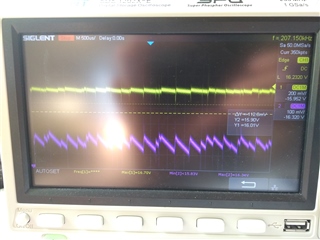

However, VPOS stays at ~16.1V when enabled instead of the target 15V. There is no short with the booster voltage, as the rail is discharged normally when disabled. There is also a small ~0.2V dropout compared to the positive booster voltage.

I tried setting the voltage adjustment register to +/-14.75V or +/-14.25V. While the VNEG rail reacts as expected, VPOS stays at 16.1V. The voltage does not change, even under load.

The issue appears on two different prototype boards.

Some insight and help would be greatly appreciated. Thanks in advance!