Dear Team,

Hi, I would like to inquire about the buck converter.

The circuit is composed as follows, and the ripple of the output voltage is as follows.

At this time,I try to keep the output voltage ripple within 36mV which is 2% of 1.8V.

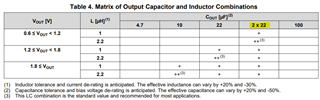

In order to reduce the voltage ripple, the inductance of the switching part was reduced and the bulk cap was enlarged.

Also, I tried to reduce the ripple by increasing the crossover frequency by increasing the feedback cap to speed up the reaction speed of duty change, but to no avail.

One). May I ask if there is another way to reduce the dip voltage as shown in the picture?