Hi Team,

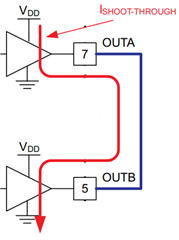

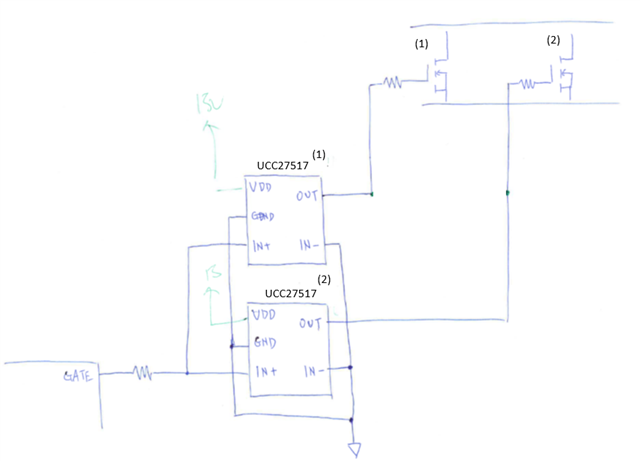

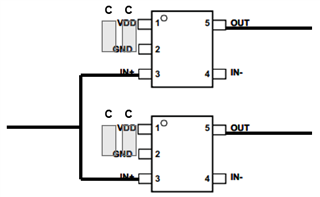

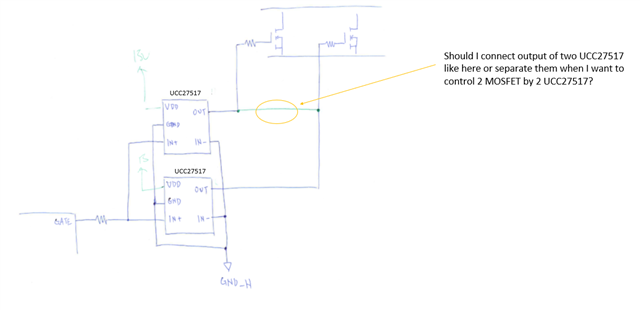

My customer wants to know should they connect output of UCC27517 together or not when driving 2 MOSFET by 2 UCC27517,

could you kindly help confirm it and let me know the reason of your answer? Thanks.

Please let me know if you need more information from customer.

Regards,

Jo