Other Parts Discussed in Thread: TIDEP-01002, TIDEP-01022, CSD18563Q5A

I am using LM5141 as the first stage voltage regulator to output VSYS_3V3 and TPS61088RHL as the second stage boost to output VSYS_5V0, and refer to the TIDEP-01002 and TIDEP-01022.

TIDEP-01002 Schematic TIDEP-01022 Schematic

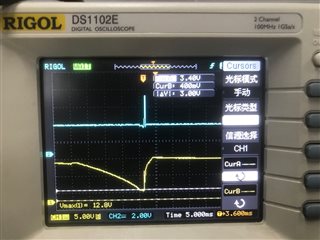

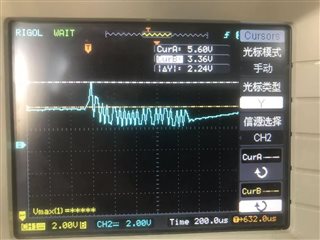

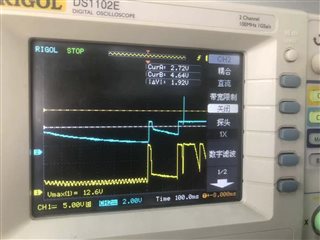

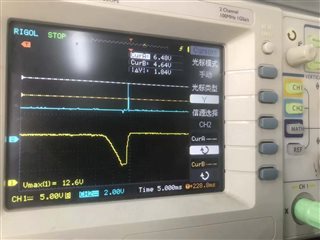

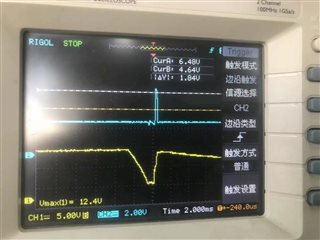

Overshoots occurs on VSYS_3V3 when the power supply in a special condition like quick off/on.

No direct issue happens related the overshot on VSYS_3V3, but it makes VSYS_5V0 having the same overshoot too, the overshoot on SYS_5V0 may be up to 8V.

So issues happened on the device supplied by SYS_5V0, it will cause the CAN PHY broken since CAN PHY‘s VCC is supplied by SYS_5V0, and it also makes LM5141 being damaged since VCCX is connected to SYS_5V0.

To avoid the device to be damaged again, we put a 5.1V zener-diode on VSYS_5V0 to protect the device , but that's just a "Patch" not a good solution to solve the issue.

Any one who can help to to analyze the issue and help me to make the VSYS_3V3 to be a better performance when the power supply in quick off on conditon.

Thanks

Best regards

Yantao