Hello,

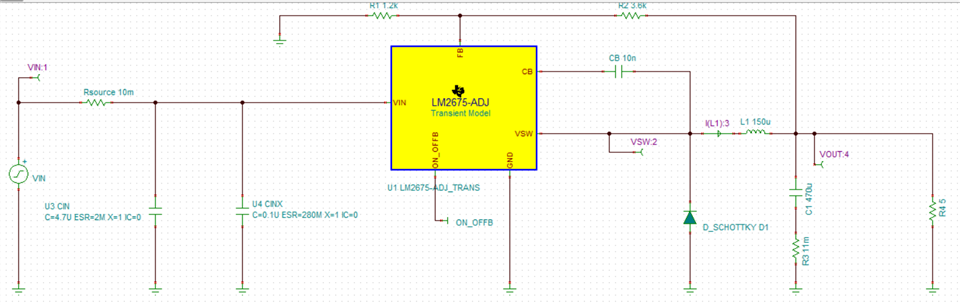

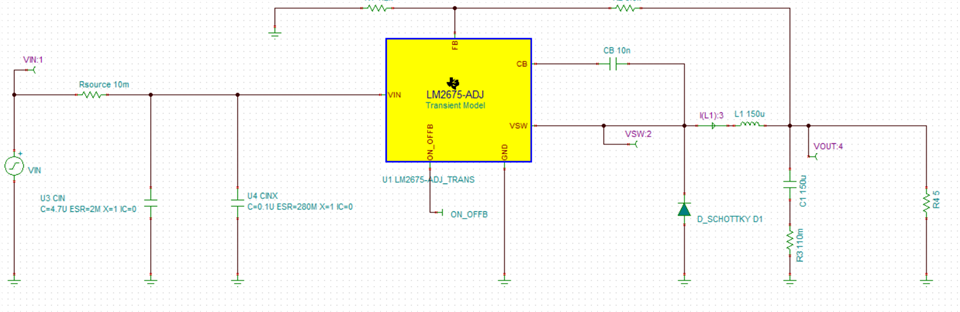

We are using the LM2675MX-5.0 NOP as a 5V/1A buck regulator, with 150μHy inductor and 470μF/10V/70mΩ aluminum output capacitor.

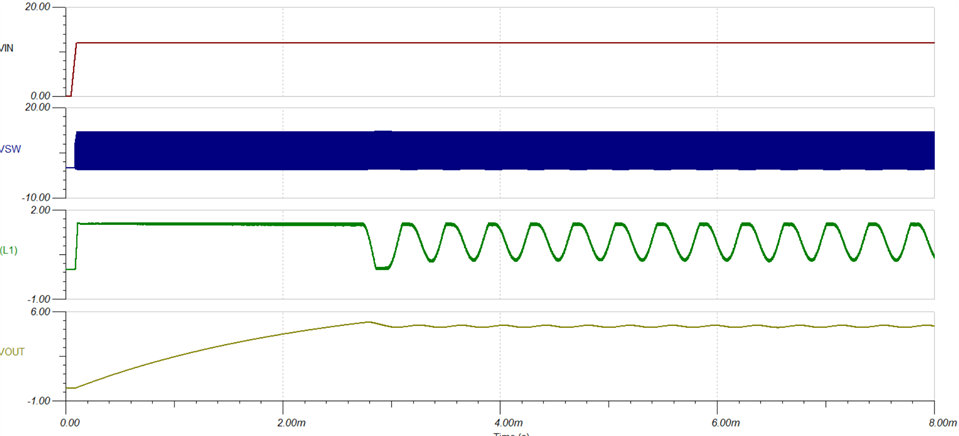

Due to capacitors allocation problem we want to use 470μF/10V/11mΩ polymer capacitor.

The datasheet of the LM2675MX-5.0 NOP states that when using 150μHy inductor, the output capacitor should be 120μHy/35V with ESR of 117mΩ or 140mΩ, depends on which manufacturer is chosen (tables 7 and 8 at the datasheet).

Also, it is stated that when not using the suggested output capacitors, the parameters of the chosen capacitors should be as close as possible to the suggested capacitors, with emphasis to ESR (page 21 at the datasheet).

My questions are:

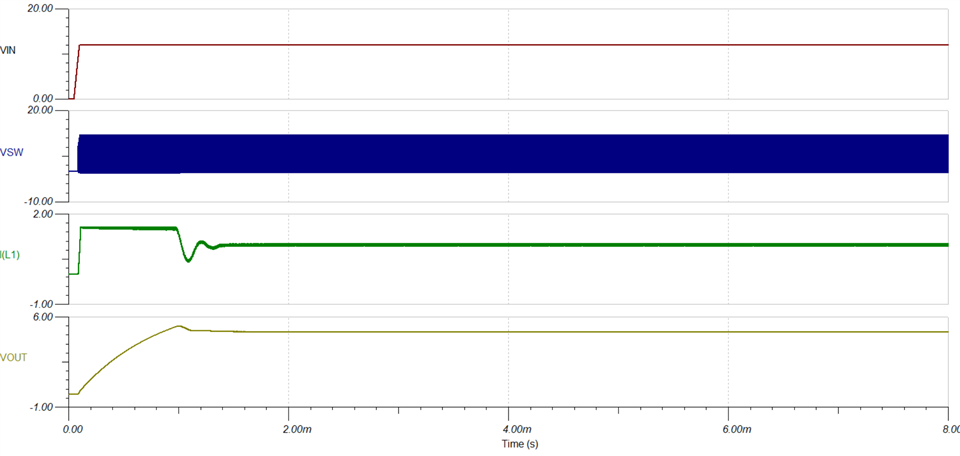

- Can we use the 470μF/10V/11mΩ polymer capacitor in our application?

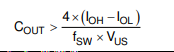

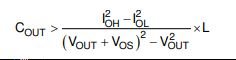

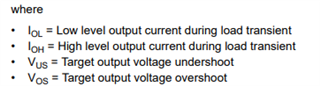

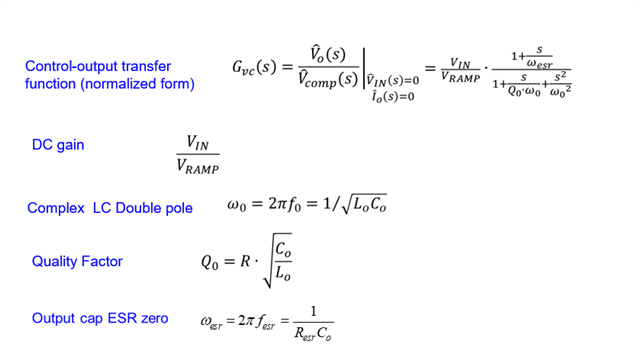

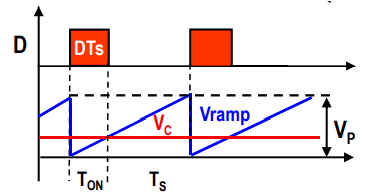

- What is the importance of the output capacitor ESR, and what is the minimal ESR that can be used?

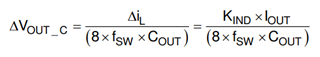

- How can I determine what is the needed ESR for the output capacitor?

- Is there a reason that the datasheet states the output capacitor as 120μF?

- Is there a relation between the output capacitance and the needed ESR?

Thanks,

Asaf