Hi team,

Recently I 've been testing the TPS54620EVM and want to figure out the EC table specs . Here I have some confusion about the EC table specs shown in the section 6.5, page 6~7in the corresponding datasheet .

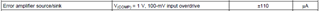

1. What does the error source/sink current mean ? How about the testing condition ?

Current sourcing and sinking to the in-phase end ?

Current sourcing and sinking to the in-phase end ?

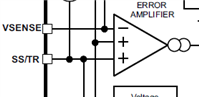

2.What does the ss/tr to Vsense matching means ?

![]()

3. Also I have some confusion about the FB resistors setting . Why larger resistors are required in order to improve the efficiency at light loads ?

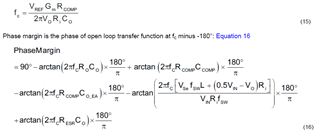

I have read the technique article of "Loop Response Considerations in Peak Current Mode" ,as is said , the worst phase margin happens at minimum Vin and minimum Io . However from the Phase Margin equation , the phase margin is independent of Io . Can you give me some guidance and advice ?

Thanks a lot for your support !