Hi Sir,

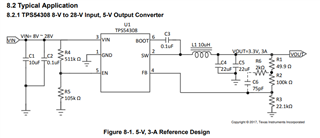

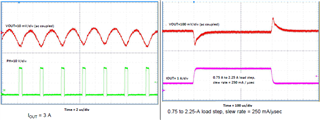

I now use tps54308. If the feedback phase compensation capacitor C6 is used on the designed substrate,

it is approximately more than 50pF,

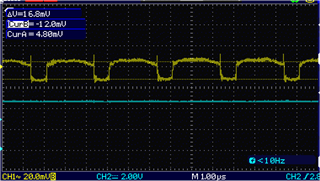

Does the protection circuit work when the power is turned on? Unable to output normally.

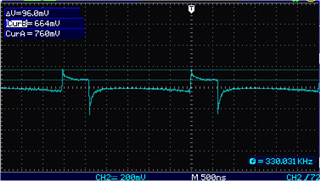

Correctly, it is temporarily off after tens of pulses SW,

Send dozens of pulses off.

Please tell me the reason.

It seems to be turned off due to abnormal voltage detection of FB terminal.

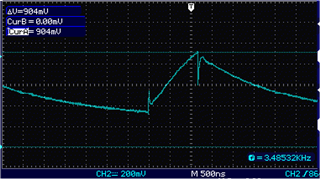

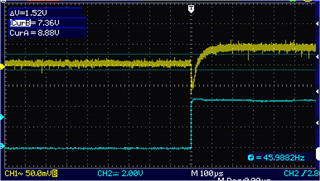

On DSO, it turns into a triangular waveform with a peak value of about 0.9V, so it seems to be protected.

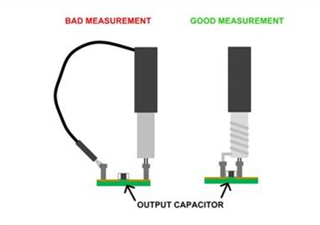

Under this condition, when the DSO probe of FB terminal is equivalent to 1:1 and about 10PF is inserted between GND,

Because no delta voltage is generated and no protective measures are taken, I think C6 is carried out too much or the gain becomes high.

Therefore, I think the C6 value will change according to the pattern layout.

is it correct?

Thanks for your clarification.

Regards,