Hi team,

Please check if my following understanding is correct or not:

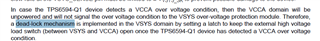

1. The reason for OVPGDRV can be recovered after the overvoltage condition is clear is because VSYS Monitor is supplied by VSYS and it continuously monitor the VSYS, right?

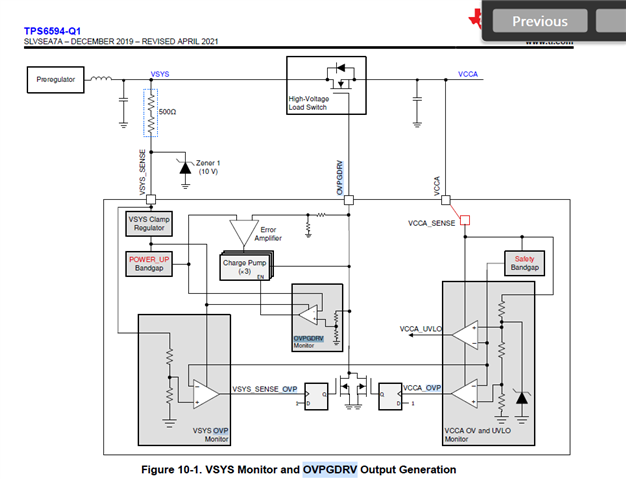

2. After OVP is triggered, it is mentioned that chip will go to safety mode and a lock-up bit will be set, right? Is the bit VSYS_LOCK_EN?

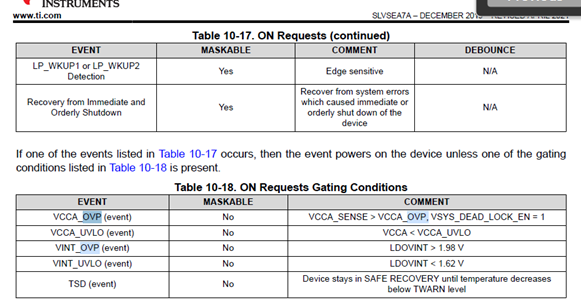

3. How to recover from the safety mode(in this case: OVP is triggered)?

4. it is mentioned in the datasheet that if VCCA stays above OVP threshold, the device will stay in SAFE RECOVERY state until supply power cycle occurs, However, when in safety mode, VINT is power down, how can I know if the VCCA is OVP is cleared or not? This part confused me a lot.

B&R

Lijia