Hi Experts,

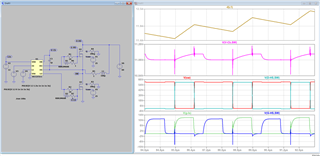

I'm simulating a half-bridge setup using UCC27211. For the FETs used, Cgs=4.7n, Cgd=1.8n, Cds=6.9n (all at VDS=0v). I'm observing unusually high spikes in Vgs-LS, Vgs-HS in LTSpice simulation. Following is the sch and waveforms

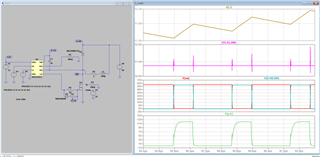

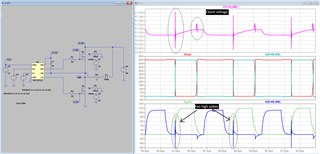

Load current is around 11.5A. I'm aware of miller effect but I dont think it'd be this severe. I connected a diode-resistor nw across 10ohm to provide a turn-off path. Following is the sch and waveforms of that -

The effect is still abnormal. The current is 11.5A here too.

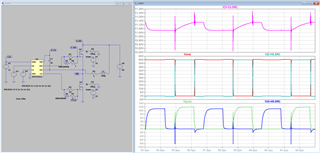

Does this have something to do with the Spice model of UCC27211? What's causing the issue? Miller effect induced spikes shouldn't be this high, esp at the given voltage, current (60v, 11.5A).