Other Parts Discussed in Thread: TPS61022

Hi,

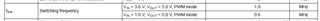

This question could pertain to any boost although I'm using TPS61022 and TPS61023 in two designs so might as well focus on them.

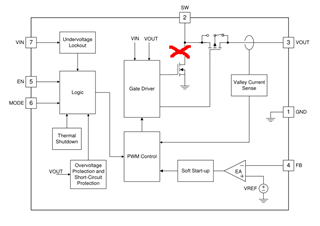

For a boost, in the situation where the input voltage is too low to create the requested output voltage (at a given current) the low FET's go to a duty % which actually causes the output to drop. The duty then continues to increase and the situation becomes worse shorting much of the current through the FET and yielding heat which usually destroys the IC. What measures do the 61022 and 61023 employ to stop this situation occurring? I use these chips specifically because they're both suited for super-capacitor use where the input voltage is low but current potentially extremely high.

Cheers, Andrew