Hi Team,

Please see my test and simulation data below. My questions are:

1. Will the CSD17313Q2 simulation model accurately predict Crss in the datasheet?

2. Is there a method to accurately predict the miller plateau voltage with different Vds values? My test results match the PSpice simulation, however figure 4 in the datasheet is higher.

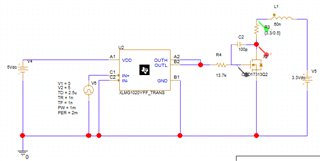

I am using the CSD17313Q2 in a resistive load application. I am using the LMG1020YFFR as the gate driver. In this test data my series gate resistor is 13.7k ohms, although I have test data for smaller and larger values if we need it. The PSpice simulation snapshot is shown below, however I need to add 100 pF miller capacitance to get the simulation to line up with the measurement. I have purposely eliminated the PCB parasitics where I could, however did not notch out the internal layers underneath the MOSFET as I anticipated just 5-10pF of interplane capacitance. I am surprised that I need 100pF additional Crss in the PSpice simulation to match my test data.

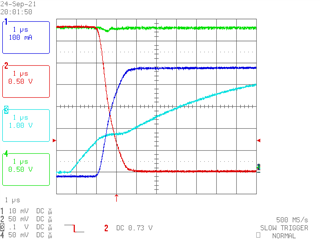

Channel 1 = Blue = Ids

Channel 2 = Red = Vds

Channel 3 = Light Blue = Vgs = 0V to 10V

Channel 4 = Green = 3.3V

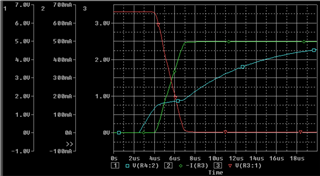

The simulation below shows the results with 100pF added as shown in the schematic.

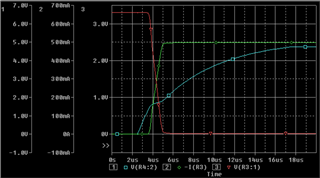

The simulation below shows the results without any additional capacitance added.

Thanks,

Stephen