Hi Sir,

To improve EMC products,

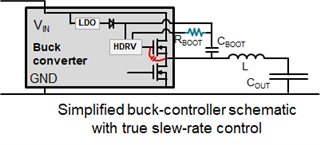

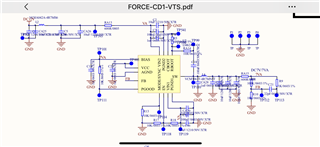

They connected a 10 ohm resistor between R boot and SW of lm62440-q1 chip,

And the SW pin is directly connected to the ground and has a 10pF capacitor,

In addition, a 4.7 ohm resistor is connected in series between C boot and R boot.

Does the above affect the circuit function?

R5 = 4.7 Ω, ra14 = 10 Ω, ca28 has been changed from 1NF to 10PF.

The problem now is that when the customer's products fluctuate at low pressure (3V − 9V),

The chip temperature is very high, and there is a chance of short circuit. After changing R5 to 0 Ω, the temperature is normal,

However, we are not sure about the impact of ra14 and ca28 on the design, so we would like to hear your suggestions.

Thanks.