Other Parts Discussed in Thread: LM5121, LM2766

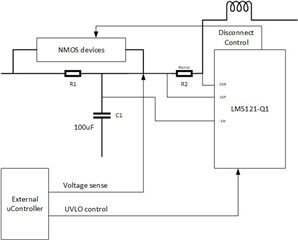

I would like to use the disconnect FET as an inrush limiter to the input capacitor. That means that the FET would be before the input cap and the Vin/SCP connections. Will this work or can it be made to work (with addtional circuitry)?