HI

We are using TPS16632 in our design and our customer have a question on PGOOD signal

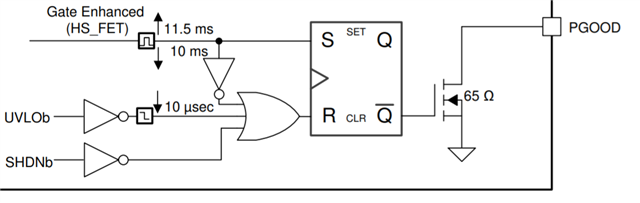

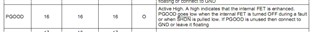

according to DataSheet 9.3.8 ( pls ref to below figures), it says that:

"PGOOD goes low when the internal FET is turned OFF during a fault event or when #SHDN is pulled low"

Actually there are no detail description on detection condition/ criteria for the * Fault event" ( Like OVP or OCP protection? the trigger condition is ?Volt or ? Amp? )

can you help to advice the detail ?

thank you

steven