Hi,

Harrison Overturf helped a lot in analyze what is the issue we are experiencing. That thread is locked, so I have to start a ne one. Here is the link to the original thread https://e2e.ti.com/support/power-management-group/power-management/f/power-management-forum/1031936/lmr33630-based-step-down-converter-burns-occasionally/3823571.

We have finished a redesign of the converter layout. It would be great if you could:

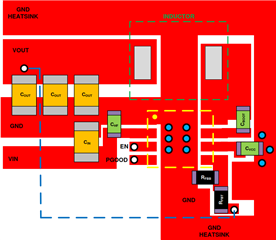

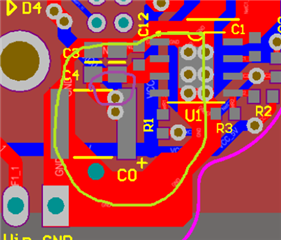

1. Please share your general thoughts if you see any potential issue in this layout, or if you have any additional recommendation.

2. We realized GND planes on input as suggested, but now there is a GND loop (marked with green line on the image) that could potentially act as antenna (we have a WiFi and RF antenna nearby). Do you see any issues there?

3. Should the input capacitors be connected with a solid plane, or to leave it as on image (marked with purple line)?

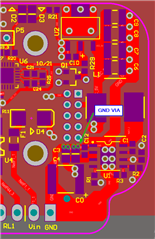

Here is the layout (Both layers, Top layer only, Bottom layer only):

Thank you,

Ivan Petrusevski