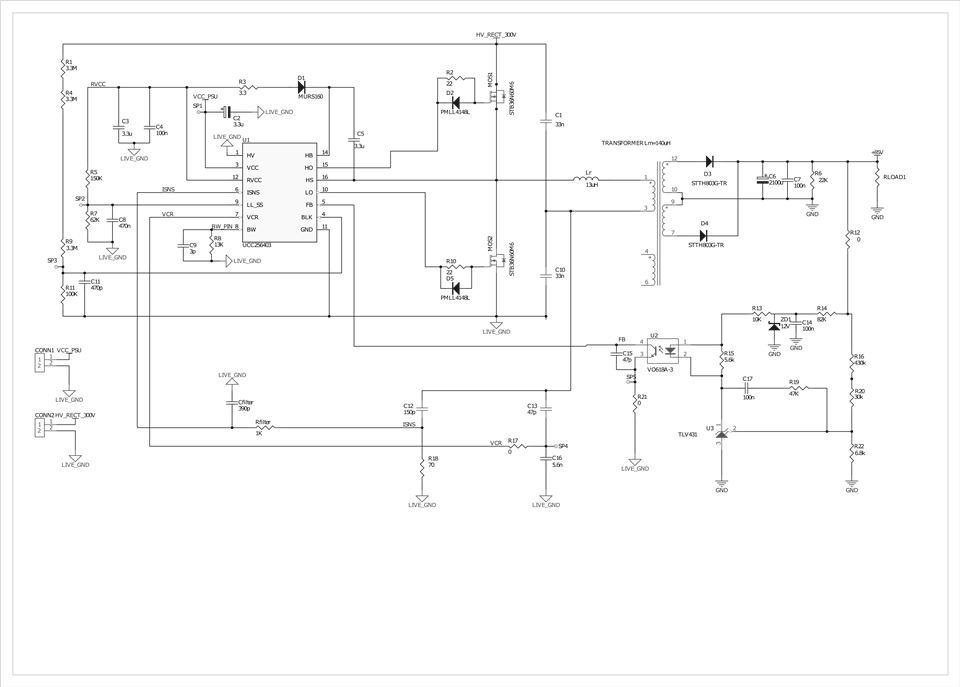

We follow your recommendation and move to the UCC256403 (https://e2e.ti.com/support/power-management-group/power-management/f/power-management-forum/1042317/ucc256303-skipping-pulses?tisearch=e2e-quicksearch&keymatch=ucc256303). Please, refer to that thread for more details about our application and specs (VIN = 240...380V, VOUT = 85V, POUT,MAX = 600W, option 3 selected on BW pin).

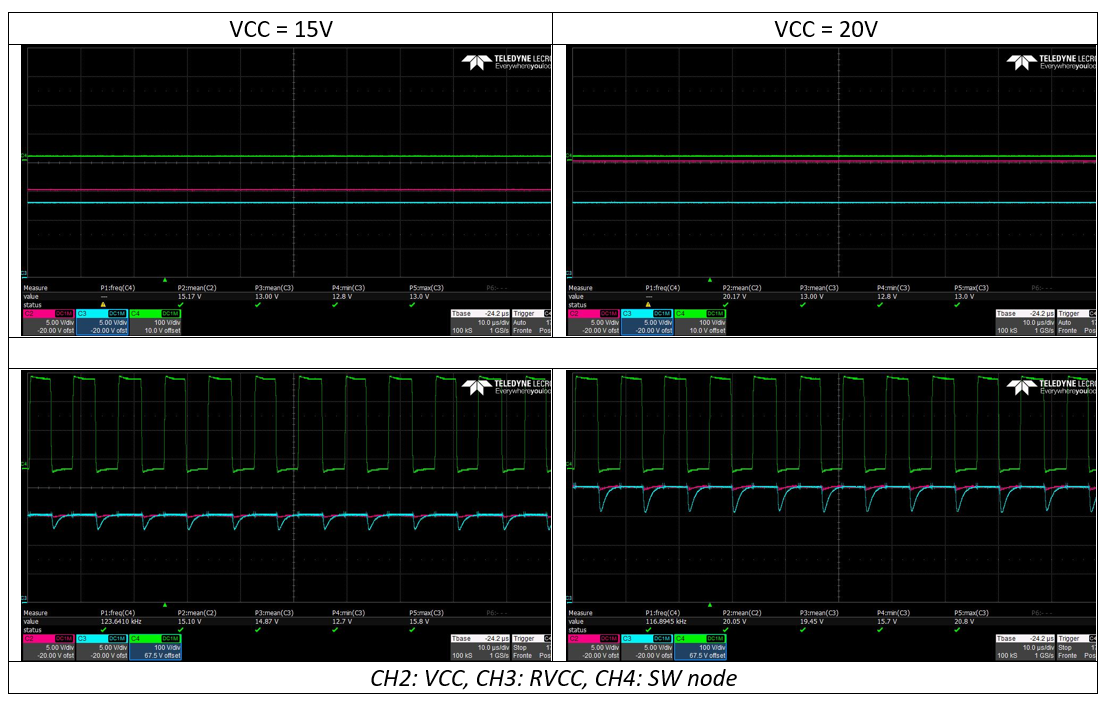

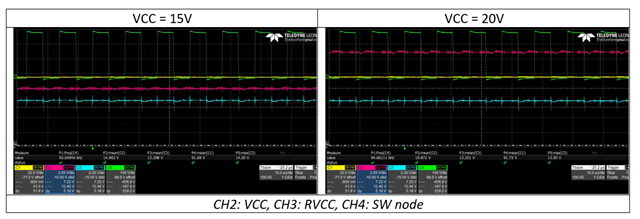

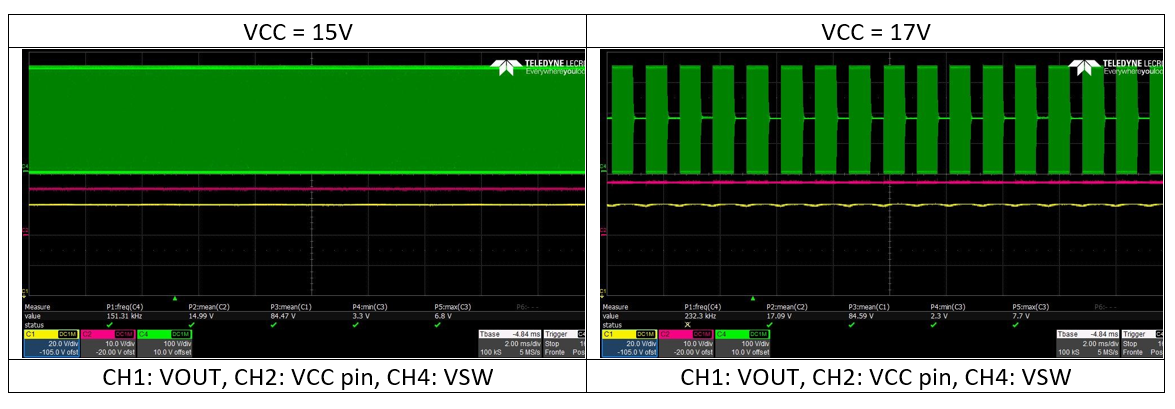

At fixed input voltage and load, converter enters burst mode when VCC > 16.5V. Scope acquisition below for 170W output power and 330V input voltage.

What might the reason behind that behaviour and how to avoid it? From the datasheet, I can see that VCC supplies the current generator of feedback pin.

But I didn't expect supply voltage to affect the overall feedback chain.

The same burts mode happens (at VCC = 15V) also if bulk voltage goes above 340V.

Kind regards