Other Parts Discussed in Thread: TPS56221,

Hi TI Team,

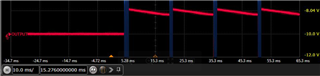

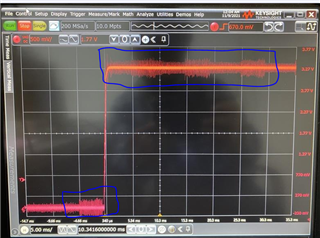

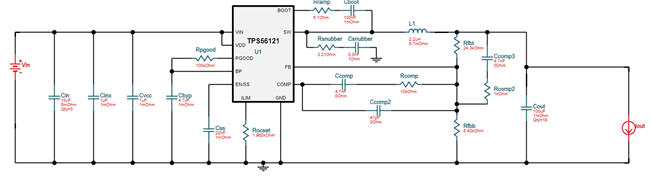

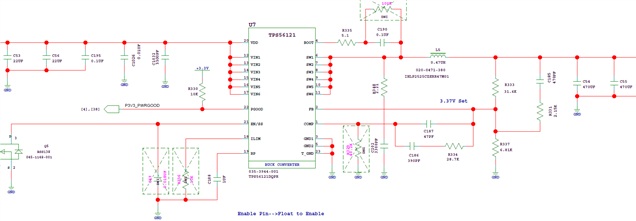

Like similar case we kept our product turn-off for more than 1 hours (we called it as Cold start), we are using TPS56121DQPR to generate 3.3V from 12V input, Problem occurs when we use 6.8nF as soft-start capacitor and 1.21K as RIlim (Current limiting resistor), we observed 3.3V is not generating, it is showing 1V in DMM. we had tried with different soft start capacitor value and current limiting resistor like 1.) 33nF and 1.21K. 2.) 33nF and 2.21K. 3.) 6.8nF & No current limiting resistor. 4.) No soft-start capacitor and 1.21K as current limiting resistor. With above 4 combinations we don't find any issue of cold-start but why the combination of 6.8nF and 1.12K getting failure in cold-start. In our design this 3.3V rail is going to so many devices and due to this the accumulation of total capacitance on output of the regulator becomes around 1700uF. Our design in the below image:

Early response would be quite appreciating.

Thanks