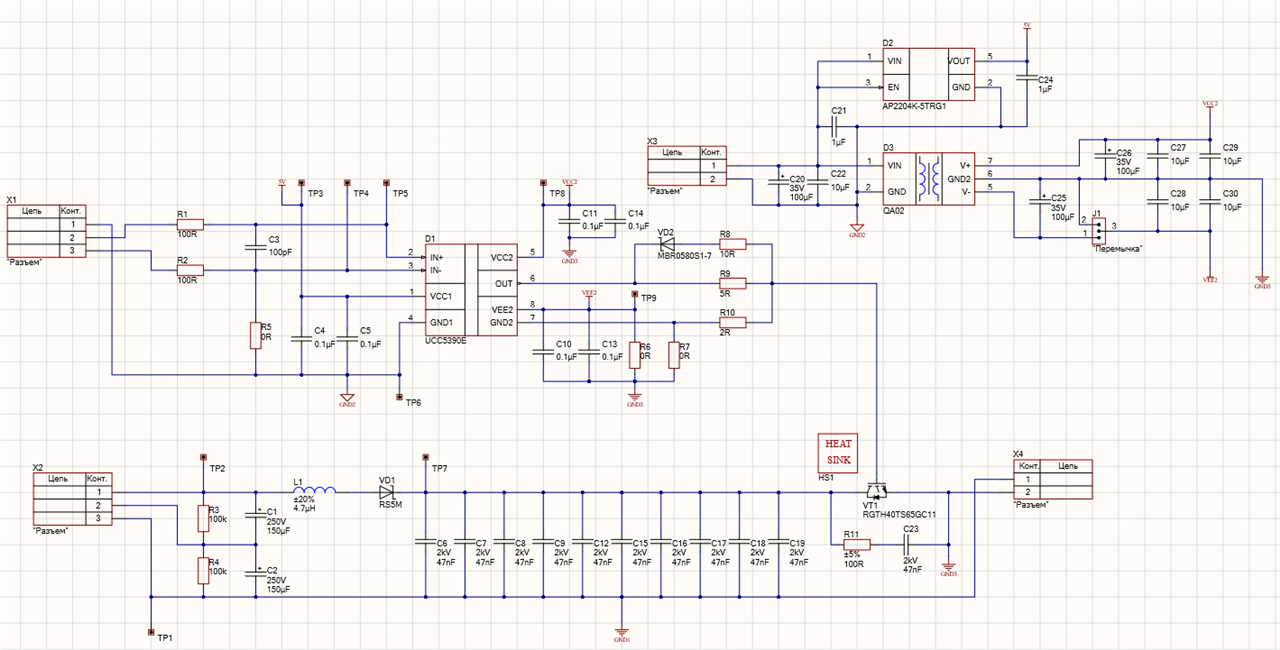

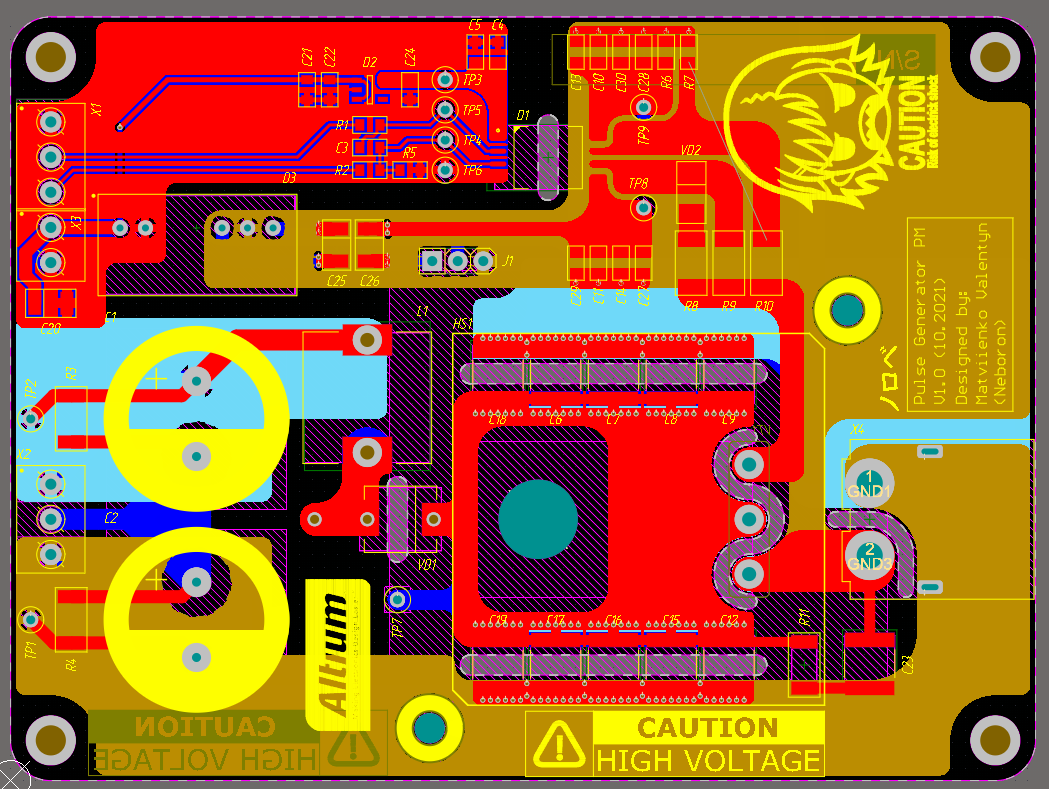

Hello! I made a custom evaluation board to make some tests of UCC53xx drivers for my applications. Below you can see the first variant of the board with UCC5320C (Ron = 10Ω, Roff = 5Ω, VCC2 = 16V, VCC1 = 3.3V). In the first test, load capacitance was equal 1nF, I feed a square wave on IN+ (IN- connected to GND1) with duty cycle 50% and I got a nice result, low rise and fall time, high duty stability on a wide range of frequencies, etc. But when I increased load capacitance to 4.7nF I obtained just noise on the driver output (see oscillogram below), very unstable duty cycle, and frequency, and even when the load capacitor was disconnected noises have not disappeared, it looks like I burned the driver. The result was the same for UCC5390E (with another scheme configuration for this driver). Do you have any suggestions on what could have gone wrong?