Other Parts Discussed in Thread: TPS7A33, LMZ31704, LM27762, TPS7A39, TPS65131, TPS7A91, TPS7A47, TPS7A52, LM27761

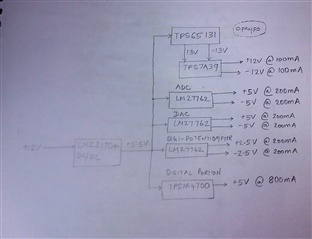

I am designing a power supply circuitry for the analog front end of my isolated data acquisition module.

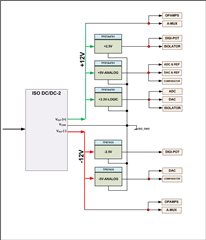

- The inputs are isolated +12V and -12V from an isolated DC/DC convertor

- The supply voltages required are +5V,+2.5V,+3.3V and -5V,-2.5V

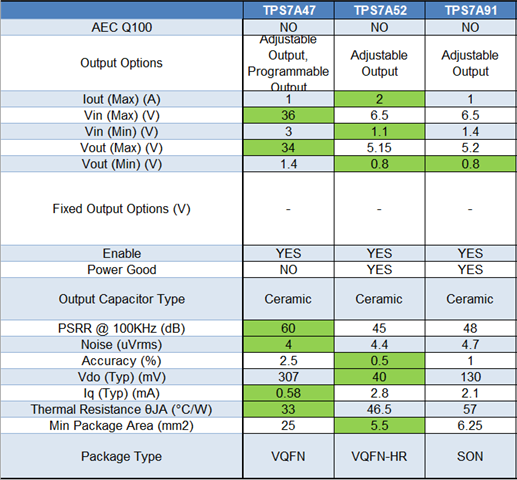

- I am planning to use TPS7A4701 and TPS7A33 for generating various positive and negative voltages

- The planned configuration is attached here with

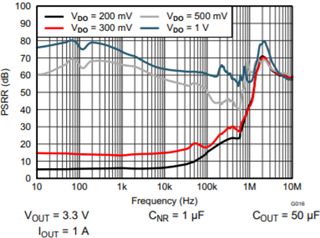

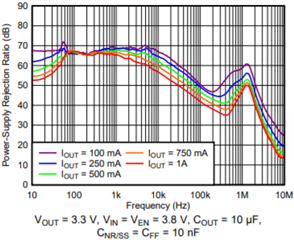

- As per the datasheet (SBVS204F:page-20) ,the power dissipation is "Power dissipation in the regulator depends on the input to output voltage difference and load conditions. PD can

be calculated using Equation 7 . - So my question is whether TPS7A4701 / TPS7A33 can be used for generating voltages,when the difference between input(12V/-12V) and required output voltages(+5v,+3.3V,+2.5V) are high

Just adding one more point: all output voltages have load requirements of around 700mA

Regards,

Chandru