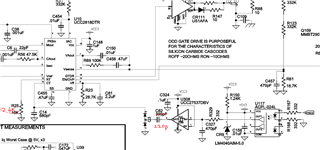

Hello there, I am looking for insight on the problem I am experiencing with the UCC2818.

The problem appears when I put load on the output while synchronizing the controller.

Figure 1: Instability at load with synchronization (1A output)

Channel 1: rectified AC voltage

Channel 2: AC current

Channel 3: inductor current

Channel 4: Ct voltage

Figure 1 shows the response when 1A load is applied. You can see that for some reason there is a peak in the current and voltage waveform.

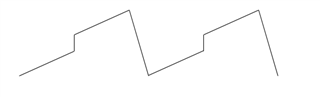

Figure 2: Zoomed-in of figure 1

Figure 2 shows a zoomed in picture at the peaking section. It can be seen that there is nothing wrong with the voltage across Ct.

I tried disconnecting the sync and just let the controller free run and there was no problem at the same load as shown in figure 3 below.

Figure 3: Response during free run (No sync, 1A load)

I tried playing around with the capacitance needed for synchronization. By reducing the capacitance, I was able to get a stable output at 1A as shown in figure 4 below

Figure 4: Response with sync but with lower sync capacitance (1A load)

However, as soon as I increased the load to 2A, the problem resurfaced.

Figure 5: Response with sync (2A load)

I need to mention that this problem does not appear throughout the whole load range if I let the controller free-run. Is there any correlation between the sync capacitor to the operation of the controller? Any insight is appreciated.

Best,

Thien Nhien Huynh