Other Parts Discussed in Thread: CSD19538Q3A

Hi Team,

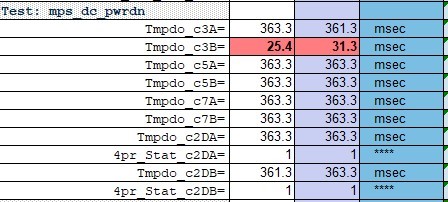

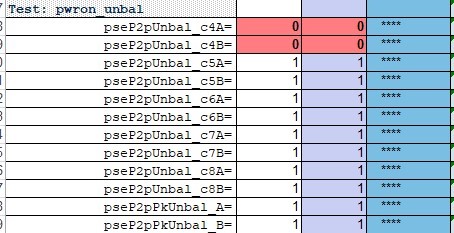

Customer is using our TPS23881 as a semi-auto mode, and found 2 fail items when running the Sifos testing that: 'PWRON_UNBAL' & 'MPS_DC_PWRDN', detail as below:

And when running the testing, customer's TPS23881 configuration is:

//Set all channels in semi-auto mode

0x12 set to 0xAA

//Enable all channel's DC disconnect

0x13 set to 0x0f

//Set 4pair ports in 4 pair 90W mode

0x29 set to 0xFF

//Enable all channels' detection and classification

0x14 set to 0xFF

And before the ports power on, the SW will detect whether this port is single PD, if yse, then will set 0x2D to enable NCTnn & NLMnn, and enable 2P ILIM/PCUT for 4P power off.

Meanwhile, per monitor the waveform when doing the 'pseP2PUNBAL_C4A ' testing, they found there is 470mA at altA & 0mA at altB, and then after ~1S, this port be power off and PSA3000 report fail.(waveform picture as below).

Base on the information above, could you kindly help to check what's the potential reason? and share us your suggestion or other items need to be further verified.

Thanks & BRs,

Cheney