What will be the VOUT when EN is held low?

Is the VOUT floating or driven 0?

If it is driven, what is the pull down resistance?

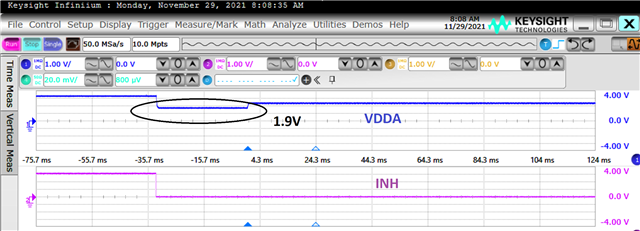

We are using this LDO for ethernet PHY DP83TC812, where we are trying to cut-off power supplies using EN of the LDO, but the supply is not going to 0V. It is saturating mid rail at around 1.5V.

We want to understand if this is a board level issue or whether LDO is floating.

Please refer to the image below, VDDA is the output of the LDO, INH is the signal connected to EN