Other Parts Discussed in Thread: CSD19537Q3, CSD18543Q3A, CSD17308Q3

Hello,

we are using the bq24715 as the main power controller of a battery buffered device. The battery uses two LiIon cells, so the system voltage is at 8.4 volts. Input voltage is 24 volts, and the circuit is pretty much the same as described in the data sheet and the EVM manual:

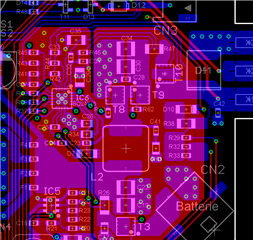

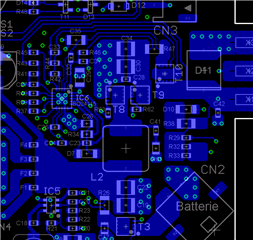

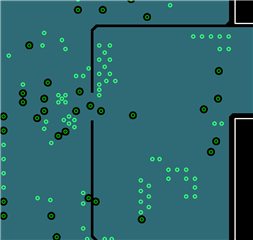

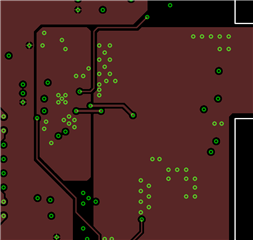

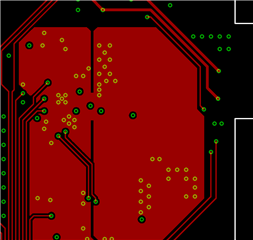

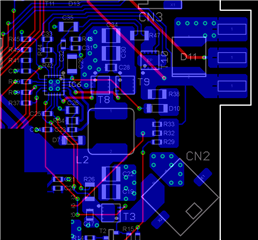

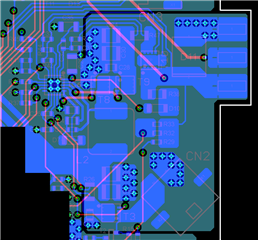

The PCB is a four layer board with this layout (outer layers only resp. all layers):

From a pilot series of 100 units, many (about 20) have already failed with a defect HS-FET in the switching regulator. We don't have any clue about what might have triggered the fails. Some units ran perfactly fine for days or weeks, and then suddenly failed. Others failed shortly after power-on.

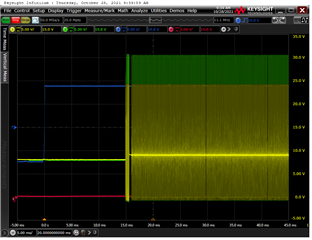

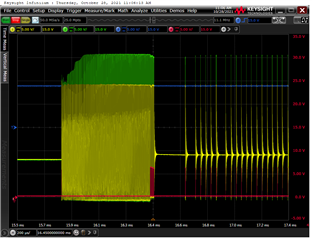

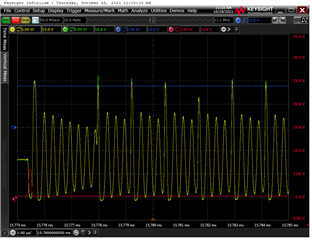

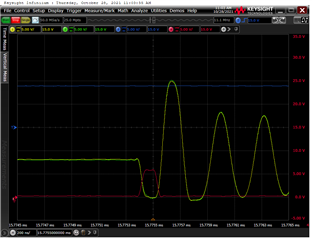

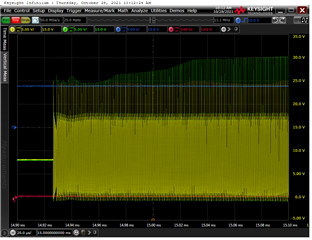

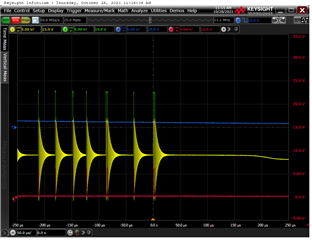

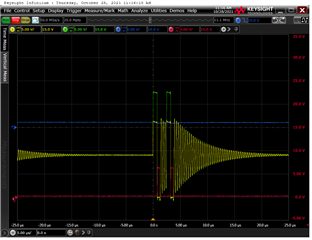

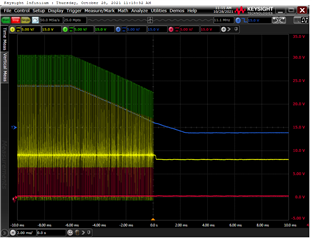

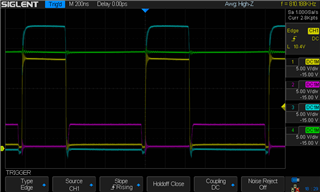

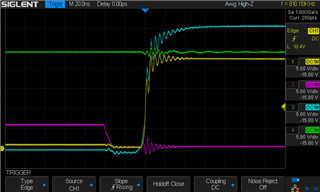

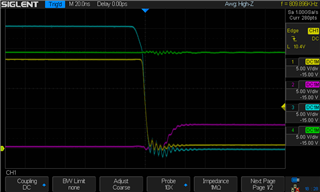

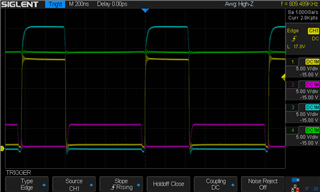

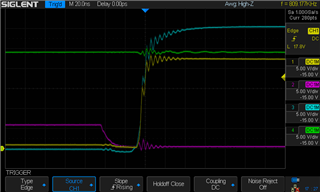

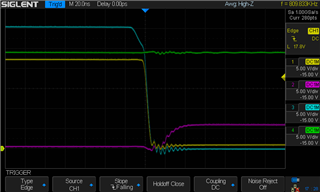

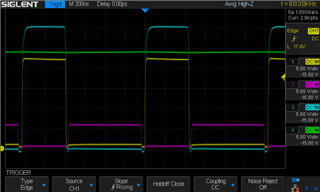

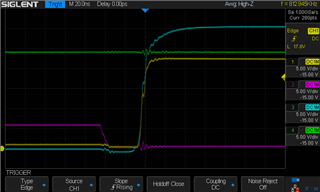

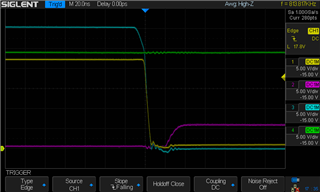

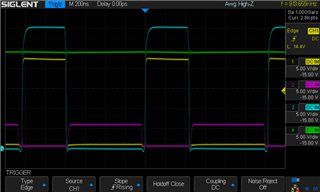

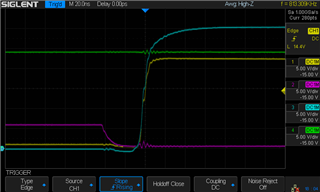

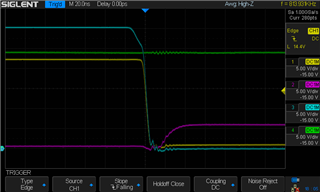

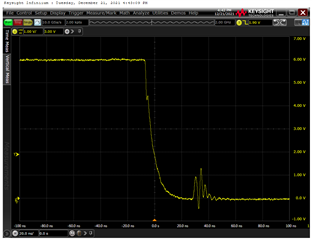

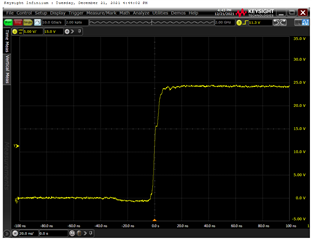

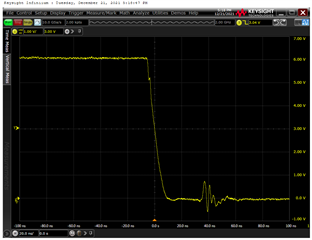

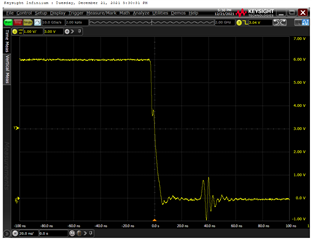

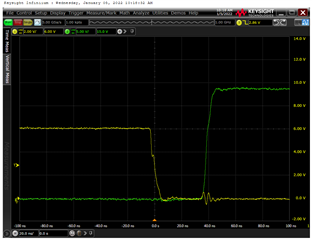

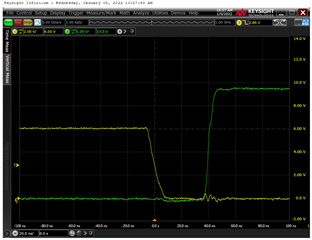

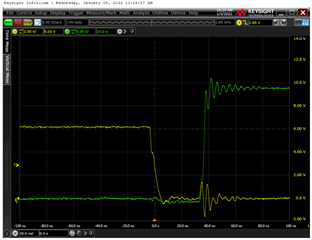

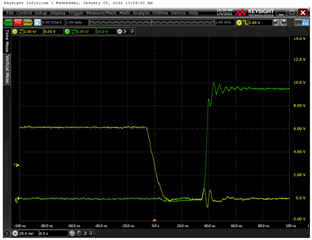

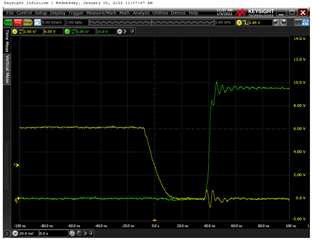

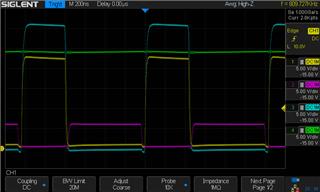

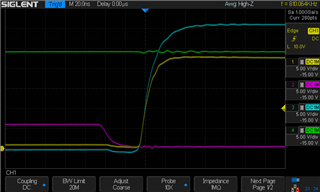

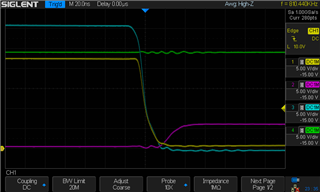

Everything that we have checked so far seems perfectly fine. Plug-in and plug-off of the 24 V supply results in perfectly correct behaviour of the regulator, and there also is no unusual thermal situation (at full load and under real working conditions within the enclosure, we measured HS-FET temperatures of about 60-70°C). Also, the switching signals appear perfectly fine with sufficient dead time:

(Signal colors are obvious, however: yellow = PHASE, pink = LS gate, blue = HS gate, green = 24V input).

We would be very glad if someone had any idea what to look for... (We don't even know if this issue should be filed under bq24715 or CSD17308...)

Thanks & regards, Tilmann