Other Parts Discussed in Thread: LM5106, TINA-TI, LM5109B

Hi Team,

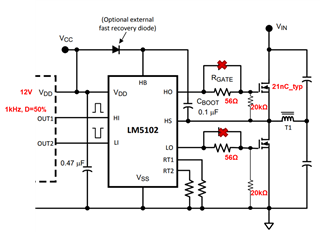

I have a simple question about LM5102 HO/LO state when VDD is 0V and 0~9V(below recommended operating conditions).

Hi-Z, pull up, pull down?

I think 0~9V is unknown state though.

Regards,

Kai