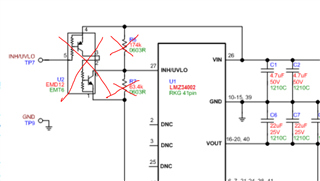

I am designing a circuit that requires the regulator to be off completely until commanded by an FPGA. I am controlling the inhibit pin with a normally closed solid state relay, such that the INH is pulled low until it's commanded to "enable". Based on the datasheet (section 12.12), it states that the INH pin has an internal pullup current source, allowing user to float the INH pin for enabling the device.

When running simulations, it seems like it doesn't turn on at all when the INH pin is floating. But when I add the two UVLO resistors with the SSR, it works as it should.

Is there an issue with the PSPICE model or the INH cannot be left open float to enable the regulator?