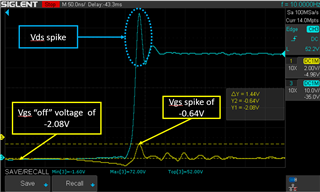

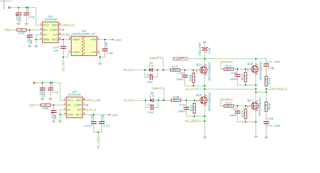

I'm having an issue where I'm implementing a negative turn off bias as described in this thread. Unfortunately I'm still somehow experiencing self turnon events despite the induced gate voltage spike being in the negative voltage region and supposedly well below the threshold voltage of the mosfets being used (VGS(th)min = 3.0V).

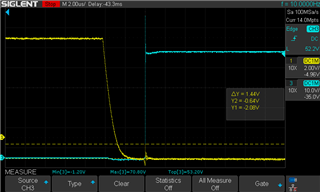

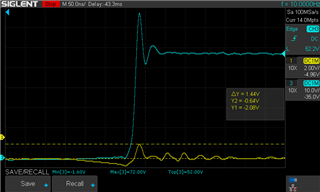

I try to focus on the turnon event(s) in the included images. Measurements were taken right where the mosfet legs enter the TO package and low-inductance measurement techniques were used with ground springs and short connections. These particular measurements are of the low-side mosfet of one of the 3 phases. The high side mosfets display similar but less severe behavior. Chanel 1 is the Gate votlage (Vgs). Chanel 3 is the switch node (Vds).

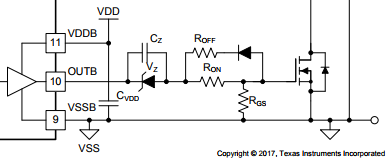

The miller clamp of the UCC5310MC device has been removed from play else it would discharge the negative bias built up by the 10uF capacitors. The clamp alone was not enough to stop the turnon events either and I've already increase the Cgs capacitor to a relatively high value.

Any ideas on what might be going on here?