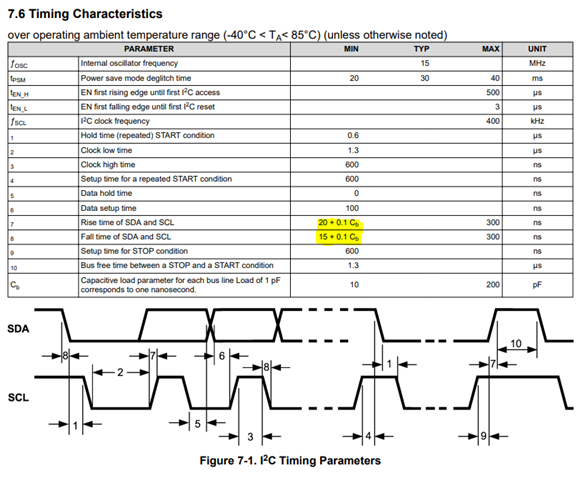

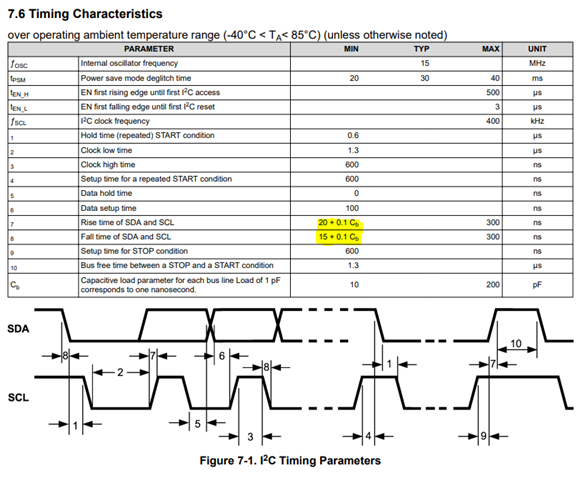

Can you advise on the performance impact if the SDA/SCL fall times are quicker than the minimum specification?

Thanks!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Can you advise on the performance impact if the SDA/SCL fall times are quicker than the minimum specification?

Thanks!

Hi Allen,

Based on our test result on EVM board, the spec has reserved some space. If the rise/fall time is within the range on datasheet, it is guaranteed that I2C communication will work properly. Please help our customer perform a board test if I2C timing is a main concern.

Best Regards,

Aaron Bing