Dear Sir/Madam,

Page 130 of the TPS53667 datasheet states that the CSP traces be routed over VREF.

I am wondering why this is required?

Can I route CSP and PWN signals between GND layers like shown below.

ie.

GND

CSP/PWN

GND

Regards Joe

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Dear Sir/Madam,

Page 130 of the TPS53667 datasheet states that the CSP traces be routed over VREF.

I am wondering why this is required?

Can I route CSP and PWN signals between GND layers like shown below.

ie.

GND

CSP/PWN

GND

Regards Joe

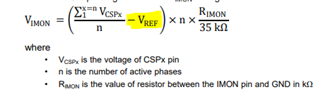

Hi Joe,

VREF pin of controller is connected to the REFIN pin of the TI smart power stages. VREF provides common-mode voltage for the IOUT signal, which is a voltage representing the output current of each powerstage. Therefore CSPx /VREF has to be differentially routed (side by side not over each other) from controller to IOUT/REFIN pin of each power stages. Differential pair PCB routing is a design technique employed to create a balanced transmission system.

The layout guidelines of the datasheet recommends following stackup :

Layer 2: Power ground

Layer 3: VIN, VREF, VOUT, PWM signals, and current sense signals

Layer 4: Power ground, analog ground, and VOUT plane

So, the stack-up in which you put the PWM & CSP signals between the two GND layers is ok. But make sure that you also add VREF island (near the controller) & VREF trace on the sandwiched layer for differential routing.

Hi,

Thank you for the reply.

I have looked at the reference design and the CSPx signals are on L3 and flood filled with VREF.

I guess this is what you mean?

Regards Joe

Yes, you can put CSPx & VREF on L3 but make sure that they are differentially routed.

Hi,

Below is from the TI EVM.It is just a flood fill.

If I run the CSPx signal over VREF they they are broadside coupled differential pairs.

This should be OK correct? I am not understanding the reason for VREF coupling.

Regards Joe

VREF acts as current sense reference voltage & That's why a tight coupling between VREF & CSPx is desired.

Some of the ways to ensure tighter coupling are:

1. To route CSPx /VREF differentially from controller to IOUT/REFIN pin of each power stages on a quiet inner layer. (Edge-coupled routes are more common, less bulkier & better coupled than the broadside coupling)

2. Create a small VREF copper plane between controller and power stages, and embed the CSPx traces inside VREF plane. (as in the EVM)

Hi,

I have limited room and flood fill is difficult unless I put three CSPx on each layer.

Below shows broadside coupling. The dielectric is 0.1mm so tightly coupled CSPx to VREF.

Broadside coupled or thre CSPx lines per layer with VREF fill. Thoughts?

L10 = GND

L11 = CSPx

L12 = VREF

L13 = GND

Regards Joe