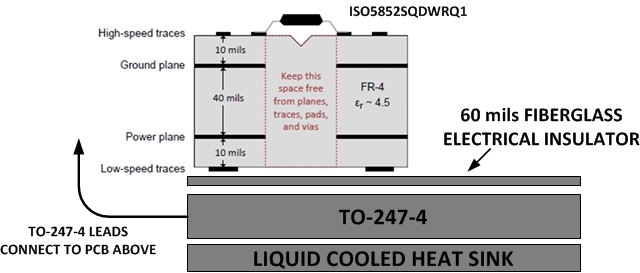

The response to the copper under the gate driver body was very interesting. I have a related question involving SiCMOS devices in a TO-247-4 package – see image. Space limitations and the orientation of the liquid cooled heat sink coupled with the goal of keeping power loop inductance and gate loop inductance at a minimum suggests a component placement as shown. What affects does the magnetic field developed by the SiCMOS have on the gate driver? Thanks, Merrill