Other Parts Discussed in Thread: UCC256301, TIDA-010015

I am using LLC (UCC256301) topology for output 24V / 20A and using UCC24612 for output stage.

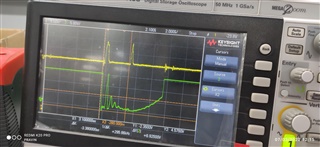

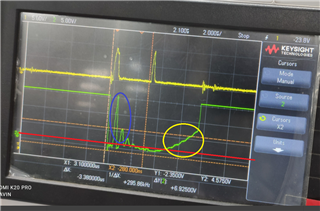

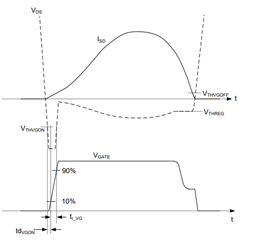

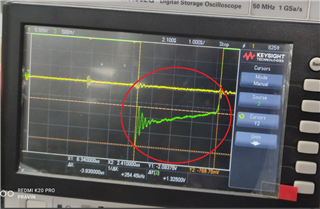

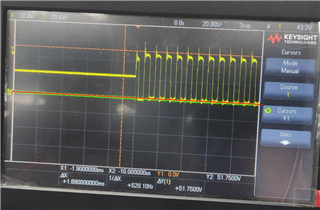

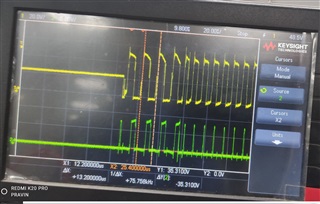

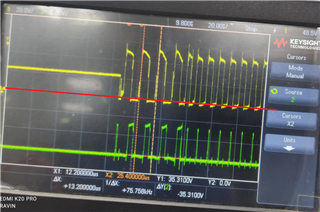

When Bulk voltage is 340 Volts, gate pulses of synchronous rectifier are present. But as soon as Bulk

voltage increases to 368V, gate pulses of synch rectifier stops. What could be the reason.

Regards

Pravin Khisti