Hello,

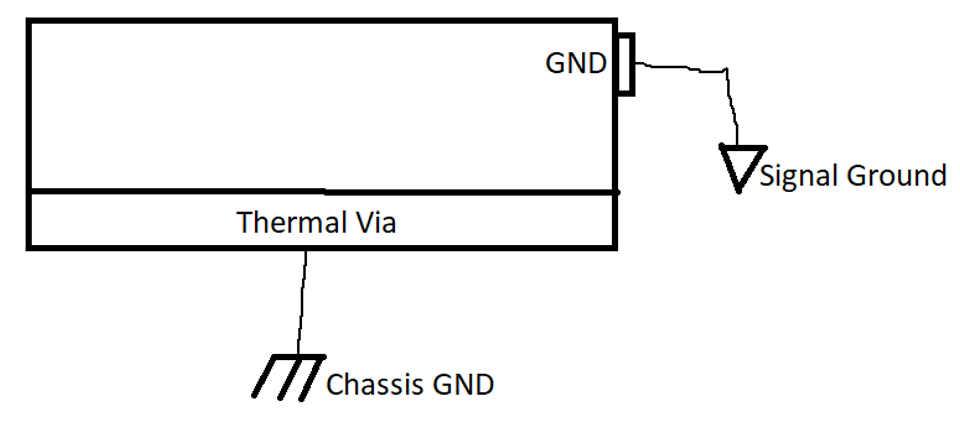

Are the GND and Thermal Via connections shorted (or resistively connected) internally to package? If not, can they be tied independently to local "digital ground" and "chassis ground" respectively?

I don't have any information of the predicted potential difference (if there is any) between chassis and signal ground. Is this configuration not recommended?

Thank you,

-Josh