Other Parts Discussed in Thread: UC1825

Hello,

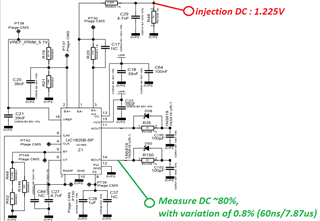

Due to instabilitty on PUSH PULL converter base on UC1825B, we investigate on the EA of the PWM driver.

We tested without power stage, with the following setup :

- EA of UC1825 is mounted in non inverter mode.

- we injected a very clean DC voltage (red figure on the schematic)

- we measured with oscilloscope variations on the duty cycle around 0.8% (60ns on the period : 7.87us)

- We respected max sink and source current of EAout.

- Output PWM can reach full range of 0-95% of the DC.

Do you have any information on this problem?

We have high voltage on the output. So the transformer have high gain, and the regulation loop is slow. So little variation on the Duty cycle cause high variation on the output voltage....

All of our power supply are clean.

We tested to add capcitor on C17, 10nF solve a part of the problem, but kill the bandwith of the loop.

Other information : If we haven't injection voltage, the PWM is in full Duty cycle (95%), because EA is in saturation mode, so in this case the output PWM is very stable, there is no variation.

Thanks for your support