Part Number: LMG3525R030-Q1

While testing the LMG3525R030-Q1 in a totem-pole PFC at low voltages (around 36V at DC side), the low side GaN FET fails. It seems that the LDO5V fails, the resistance between LDO5V and GND is only a few ohms and the GaN FET is not able to deliver 5V when powered.

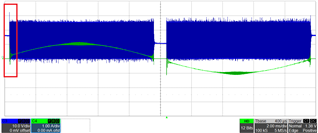

We started testing at an even lower voltage (8V) to reduce the risk of device failure and we found a voltage spike at the switch node after a zero crossing in the inductor current indicated in the figure below. This spike occurred every line cycle.

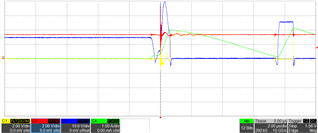

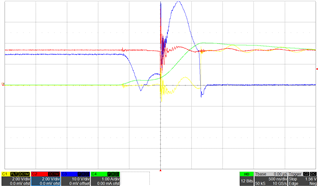

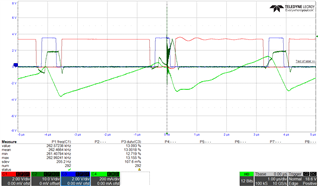

C1 is the gate signal of the low side GaN FET measured at the microcontroller

C2 is the voltage at the switch node relative from DC-, measured with a differential probe

C3 is the gate signal of the high side GaN FET, measured at the microcontroller

C4 is the inductor current

We suspect this has something to do with the ideal diode mode, but we're not exactly sure how this could happen. Could this be the cause of the device's failure?